# ENERGY EFFICIENT HARDWARE ACCELERATION OF MULTIMEDIA PROCESSING TOOLS

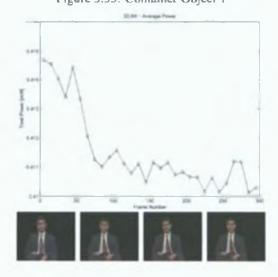

by

Andrew Kinane, B.Eng.

Submitted in partial fulfilment of the requirements for the Degree of Doctor of Philosophy

Dublin City University

School of Electronic Engineering

Supervisor: Dr. Noel E. O'Connor

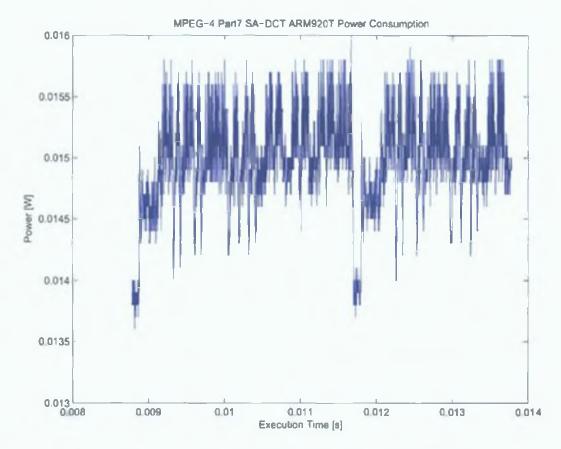

May, 2006

I hereby certify that this material, which I now submit for assessment on the programme of study leading to the award of Doctor of Philosophy is entirely my own work and has not been taken from the work of others save and to the extent that such work has been cited and acknowledged within the text of my work

ID <u>98069098</u>

Date <u>15 # Hay 2006</u>

# **Abstract**

The world of mobile devices is experiencing an ongoing trend of feature enhancement and general-purpose multimedia platform convergence. This trend poses many grand challenges, the most pressing being their limited battery life as a consequence of delivering computationally demanding features. The envisaged mobile application features can be considered to be accelerated by a set of underpinning hardware blocks. Based on the survey that this thesis presents on modern video compression standards and their associated enabling technologies, it is concluded that tight energy and throughput constraints can still be effectively tackled at algorithmic level in order to design re-usable optimised hardware acceleration cores.

To prove these conclusions, the work in this thesis is focused on two of the basic enabling technologies that support mobile video applications, namely the Shape Adaptive Discrete Cosine Transform (SA-DCT) and its inverse, the SA-IDCT. The hardware architectures presented in this work have been designed with energy efficiency in mind. This goal is achieved by employing high level techniques such as redundant computation elimination, parallelism and low switching computation structures. Both architectures compare favourably against the relevant prior art in the literature.

The SA-DCT/IDCT technologies are instances of a more general computation – namely, both are Constant Matrix Multiplication (CMM) operations. Thus, this thesis also proposes an algorithm for the efficient hardware design of any general CMM-based enabling technology. The proposed algorithm leverages the effective solution search capability of genetic programming. A bonus feature of the proposed modelling approach is that it is further amenable to hardware acceleration. Another bonus feature is an early exit mechanism that achieves large search space reductions. Results show an improvement on state of the art algorithms with future potential for even greater savings.

# Acknowledgements

This thesis would never have reached the printer but for the support and encouragement I have received from many people, some I've known for a short while, others a very long time indeed. Firstly I would like to thank Aisling, whose unwavering love has always been the key source of inspiration. I would also like to thank my parents and my sister who have been supporting me all the way through twenty plus years of schooling! Credit is due to the CDVP hardware guys, past and present, who were always willing to give encouragement and technical insights. In particular I must sincerely thank Val, who helped me through the Ph D "white nights" and convinced me that there is light at the end of the tunnel. Finally I would like to thank my supervisor, Dr. Noel O'Connor, for his guidance and support from start to finish

Courage is resistance to fear mastery of fear not absence of fear

- Mark Twain

# \_\_\_\_\_TABLE OF CONTENTS

| Ta | Table of Contents                  |                                                             | v  |  |

|----|------------------------------------|-------------------------------------------------------------|----|--|

| Lı | st of ]                            | Figures                                                     | ıx |  |

| Lı | List of Tables                     |                                                             |    |  |

| Lı | List of Peer-Reviewed Publications |                                                             |    |  |

| 1  | Intr                               | roduction                                                   | 1  |  |

|    | 11                                 | The Emergence of Mobile Multimedia                          | 1  |  |

|    | 12                                 | Grand Challenges Facing Mobile Computing                    | 1  |  |

|    |                                    | 1 2 1 Application Development Challenges                    | 2  |  |

|    |                                    | 1 2 2 Networking and Communication Challenges               | 3  |  |

|    |                                    | 1 2 3 Hardware Device Design Challenges                     | 4  |  |

|    |                                    | 1 2 4 Motivation for Thesis                                 | 7  |  |

|    | 1 3                                | Research Objectives                                         | 8  |  |

|    | 1 4                                | Thesis Structure                                            | 8  |  |

|    | 1 5                                | Summary                                                     | 9  |  |

| 2  | Tecl                               | chnical Background                                          | 10 |  |

|    | 2 1                                | Introduction                                                | 10 |  |

|    | 2 2                                | Digital Video Processing                                    | 10 |  |

|    |                                    | 2 2 1 A Generic Video Compression System                    | 12 |  |

|    |                                    | 2 2 2 Transform Theory Overview                             | 17 |  |

|    |                                    | 2 2 3 The Discrete Cosine Transform (DCT)                   | 20 |  |

|    |                                    | 2 2 4 Image and Video Compression Standards Overview        | 23 |  |

|    |                                    | 2 2 5 Object Based Processing                               | 26 |  |

|    |                                    | 2 2 6 The Shape Adaptive Discrete Cosine Transform (SA-DCT) | 31 |  |

|    |                                    | 2 2 7 Digital Video Implementation Approaches               | 34 |  |

|    |                                    | 2 2 8 Conclusions                                           | 36 |  |

|    | 23                                 | Low Power Design                                            | 36 |  |

|   |     | 2 3 1  | Circuit Power Dissipation Phenomena                          | 37  |

|---|-----|--------|--------------------------------------------------------------|-----|

|   |     | 232    | Power Analysis & Estimation Techniques                       | 44  |

|   |     | 2 3 3  | Low Power Design Techniques                                  | 54  |

|   |     | 234    | Electronic Design Automation (EDA)                           | 64  |

|   |     | 2 3 5  | Conclusions                                                  | 68  |

|   | 2 4 | Summ   | nary                                                         | 68  |

| 3 | SA- | DCT A  | rchitecture                                                  | 69  |

|   | 3 1 | Introd | uction                                                       | 69  |

|   |     | 3 1 1  | Vector Shape Parsing                                         | 70  |

|   |     | 3 1 2  | Data Alignment                                               | 71  |

|   |     | 3 1 3  | Variable N-point 1D DCT                                      | 71  |

|   |     | 3 1 4  | SA-DCT Computational Requirements Summary                    | 71  |

|   | 3 2 | DCT/S  | SA-DCT Hardware State of the Art Review                      | 73  |

|   |     | 3 2 1  | Classes of DCT Implementation Approaches                     | 73  |

|   |     | 3 2 2  | SA-DCT Specific Approaches                                   | 82  |

|   | 3 3 | Desig  | n Methodology                                                | 85  |

|   | 3 4 | SA-D   | CT Datapath Architecture                                     | 86  |

|   |     | 3 4 1  | Even-Odd Decomposition                                       | 88  |

|   |     | 3 4 2  | Reconfiguring Adder-Based Distributed Arithmetic Dot Product | 89  |

|   |     | 3 4 3  | Partial Product Summation Tree                               | 92  |

|   | 3 5 | SA-D   | CT Memory and Control Architecture                           | 95  |

|   |     | 3 5 1  | Addressing/Routing Control Logic                             | 95  |

|   |     | 3 5 2  | Transpose Memory                                             | 97  |

|   | 3 6 | Exper  | imental Results                                              | 100 |

|   |     | 3 6 1  | Fixed-Point Variable N-point 1D DCT Design                   | 100 |

|   |     | 362    | Evaluation Against Prior Art                                 | 101 |

|   |     | 363    | Conformance Testing                                          | 108 |

|   |     | 3 6 4  | System Prototyping                                           | 110 |

|   | 3 7 | Possit | ole Architectural Variations                                 | 112 |

|   | 3 8 | Sumn   | nary of Contributions                                        | 112 |

| 4 | SA- | IDCT A | Architecture                                                 | 114 |

|   | 4 1 | Introd | luction                                                      | 114 |

|   |     | 411    | Additional Complications Compared to SA-DCT                  | 115 |

|   | 4 2 | IDCT   | /SA-IDCT Hardware State of the Art Review                    | 117 |

|   |     | 421    | Classes of IDCT Implementation Approaches                    | 117 |

|   |     | 422    | SA-IDCT Specific Approaches                                  | 120 |

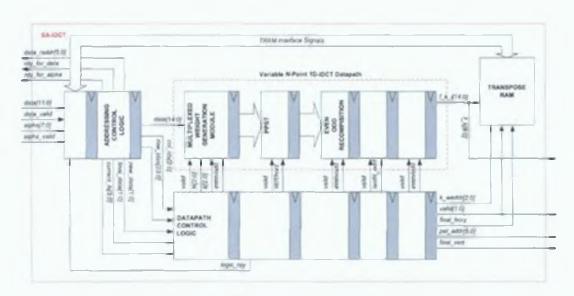

|   | 43  | SA-II  | OCT Datapath Architecture                                    | 122 |

|   |     | 431    | Reconfiguring Adder-Based Distributed Arithmetic Dot Product | 124 |

|   |     | 4 3 2  | Partial Product Summation Tree                               | 125 |

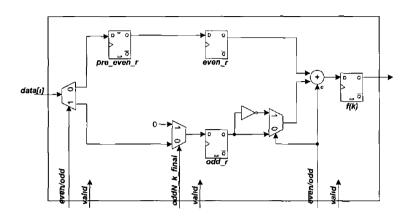

|   |     | 4 3 3  | Even-Odd Recomposition                                       | 125 |

|   | 44  | SA-II  | OCT Memory and Control Architecture                          | 128 |

|   |     | 441     | Addressing/Routing Control Logic                    | 129 |

|---|-----|---------|-----------------------------------------------------|-----|

|   |     | 442     | Transpose Memory                                    | 130 |

|   | 4 5 | Expen   | imental Results                                     | 131 |

|   |     | 4 5 1   | Fixed-Point Variable N-point 1D IDCT Design         | 131 |

|   |     | 452     | Evaluation Against Prior Art                        | 132 |

|   |     | 453     | Conformance Testing                                 | 139 |

|   |     | 4 5 4   | System Prototyping                                  | 141 |

|   | 4 6 | Summ    | nary of Contributions                               | 142 |

| 5 | Dot | Produc  | et High Level Synthesis                             | 143 |

|   | 5 1 | Introd  | uction                                              | 143 |

|   | 5 2 | Multıp  | plication by Constant Applications                  | 144 |

|   |     | 5 2 1   | Preliminaries                                       | 144 |

|   |     | 5 2 2   | Single Constant Multipliers                         | 145 |

|   |     | 523     | Constant Multiplier Blocks                          | 145 |

|   |     | 5 2 4   | Digital Filters                                     | 146 |

|   |     | 5 2 5   | The Constant Matrix Multiplication (CMM) Problem    | 149 |

|   | 5 3 | Multip  | plication by Constant State of the Art Review       | 151 |

|   |     | 5 3 1   | CMM – A Closer Look                                 | 151 |

|   |     | 5 3 2   | Optimisation Approaches                             | 153 |

|   |     | 5 3 3   | Proposed Optimisation Approach                      | 158 |

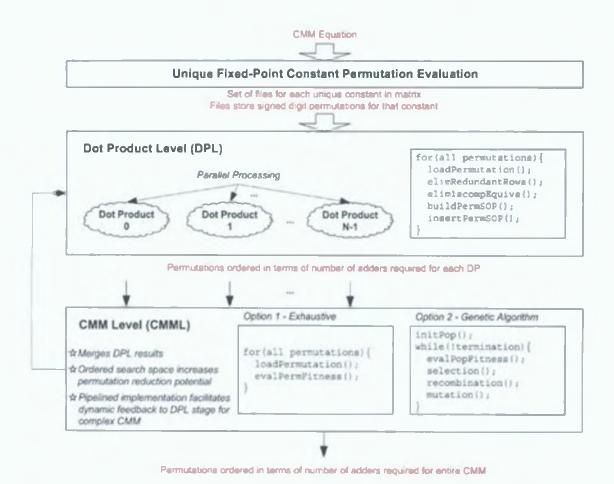

|   | 5 4 | The C   | MM Optimisation Algorithm                           | 162 |

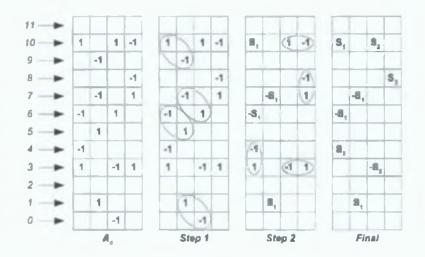

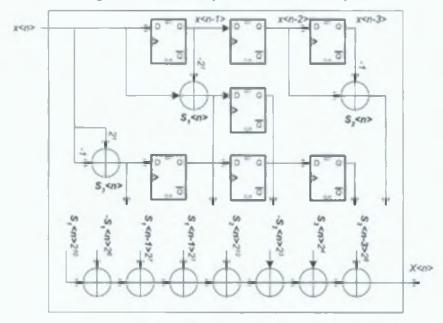

|   |     | 541     | Signed-Digit Permutation Extraction Stage           | 162 |

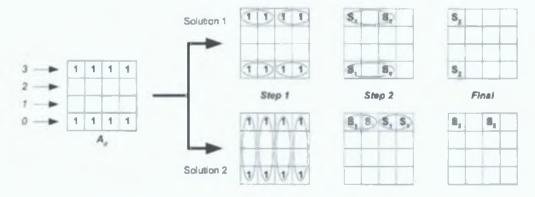

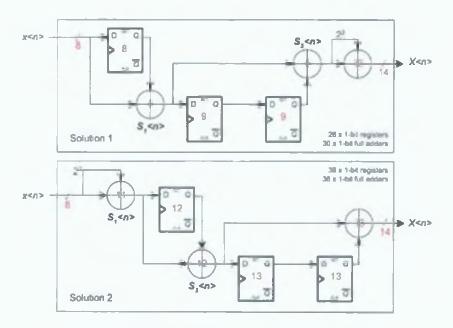

|   |     | 5 4 2   | Dot Product Level (DPL) Stage                       | 164 |

|   |     | 5 4 3   | CMM Level (CMML) Stage                              | 176 |

|   |     | 5 4 4   | CMML - A Genetic Programming Approach               | 178 |

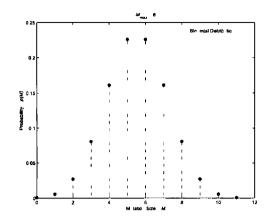

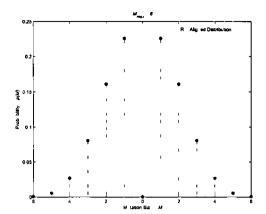

|   |     | 5 4 5   | Genetic Algorithm Parameter Selection               | 185 |

|   |     | 5 4 6   | CMML Results                                        | 187 |

|   | 5 5 | MCM     | M Extension                                         | 188 |

|   | 5 6 | Summ    | nary of Contributions                               | 190 |

| 6 | Con | clusion | s & Future Work                                     | 192 |

|   | 6 1 | Concl   | usions                                              | 192 |

|   |     | 611     | Motivation for Proposed Research – A Summary        | 192 |

|   |     | 612     | Summary of Thesis Contributions                     | 193 |

|   |     | 613     | Research Objectives Achieved                        | 195 |

|   | 62  |         | e Work                                              | 196 |

|   |     | 621     | SA-DCT/IDCT Accelerator Variations and Improvements | 196 |

|   |     | 622     | SA-DCT/IDCT Accelerator Pre/Post Processing         | 196 |

|   |     | 623     | SA-IDCT Power Efficiency Enhancements               | 200 |

|   |     | 624     | CMM Optimisation Algorithm Improvements             | 201 |

|   |     | 625     | Hardware Accelerator Adaptability                   | 203 |

|   | 63  | A Visi  | ion for the Future                                  | 205 |

| A  | Leaf          | -Labell | ed Complete Rooted Binary Trees                                            | 208 |  |

|----|---------------|---------|----------------------------------------------------------------------------|-----|--|

|    | A 1           | Introdu | action                                                                     | 208 |  |

|    | A 2           | The Pr  | oblem                                                                      | 208 |  |

|    |               | A 2 1   | Problem 1 – Valid Patterns                                                 | 209 |  |

|    |               | A 2 2   | Problem 2 – Topologies                                                     | 210 |  |

|    |               | A 2 3   | Problem 3 – Addend Permutations                                            | 210 |  |

|    | A 3           | The So  | olution                                                                    | 216 |  |

|    |               | A 3 1   | Number of Non-Isomorphic Binary Bracket Structures of n-Operand Operations | 217 |  |

|    |               | A 3 2   | Number of Leaf-Labelled Complete Rooted Binary Trees                       | 219 |  |

| Lı | st of A       | Acronyr | ns                                                                         | 221 |  |

| Lı | st of I       | MPEG I  | Meeting Contributions                                                      | 225 |  |

| Lu | st of I       | Patents |                                                                            | 227 |  |

| Bi | bliography 22 |         |                                                                            |     |  |

# LIST OF FIGURES

| 1 1  | Power Density of Silicon Versus Process Technology According to Intel | 6  |

|------|-----------------------------------------------------------------------|----|

| 1 2  | Power Savings at Various Levels of Design Abstraction                 | 6  |

| 2 1  | The 4 2 0 Image Format                                                | 12 |

| 2 2  | A Generic Video Compression Codec                                     | 13 |

| 2 3  | Intra Mode Coding Flow                                                | 13 |

| 2 4  | Zıgzag Scan Order                                                     | 14 |

| 2 5  | A Generic Video Decoder                                               | 15 |

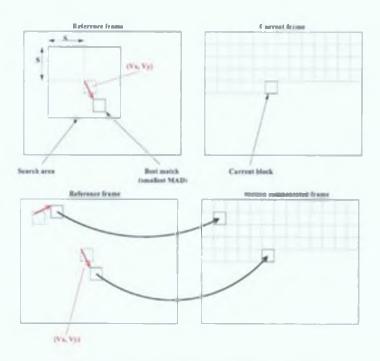

| 26   | Motion Estimation and Compensation                                    | 16 |

| 2 7  | DCT-II Basis Functions for $N = 8$                                    | 22 |

| 28   | Basis Images for 2D DCT-II with $N = 8$                               | 22 |

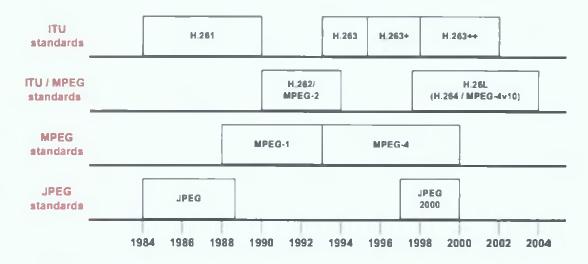

| 2 9  | Evolution of Video Coding Standards by the ITU-T and ISO/IEC          | 24 |

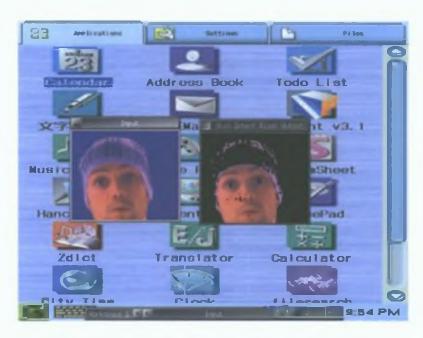

| 2 10 | Mobile Telephony Application - Human Face is Object of Interest       | 28 |

| 2 11 | Example Face Detection Based on Colour Filtering                      | 29 |

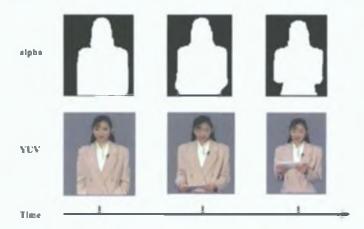

| 2 12 | Three Successive VOPs with Alpha Masks of a VO                        | 29 |

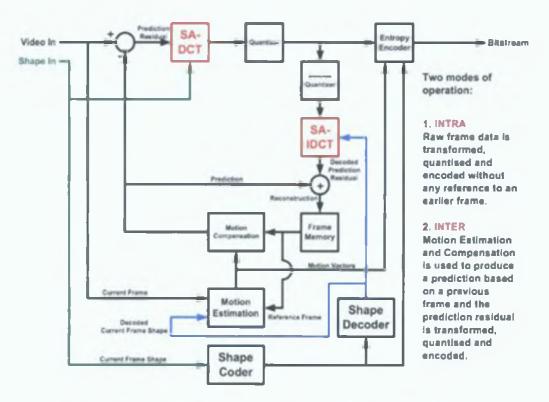

| 2 13 | A Generic Object-Based Video Compression Codec                        | 30 |

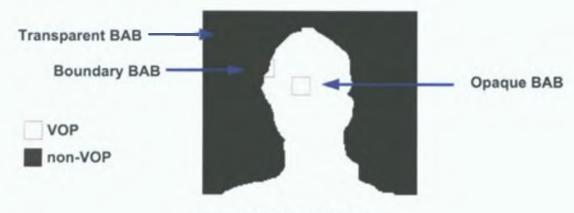

| 2 14 | Various BAB Types                                                     | 30 |

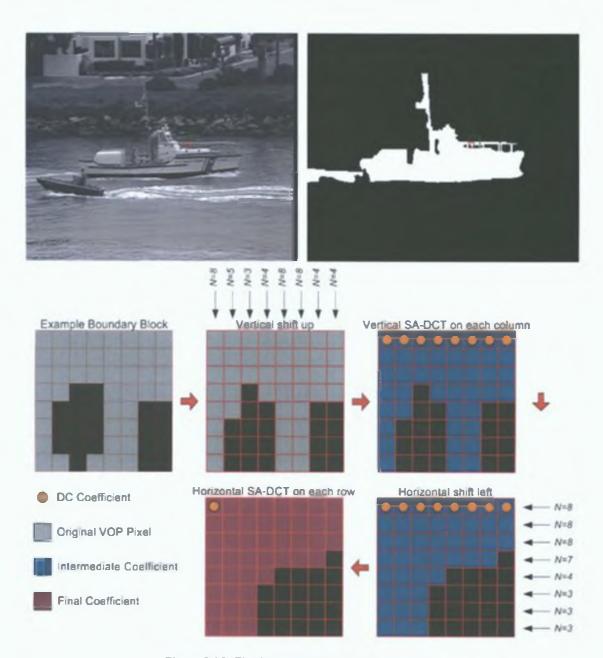

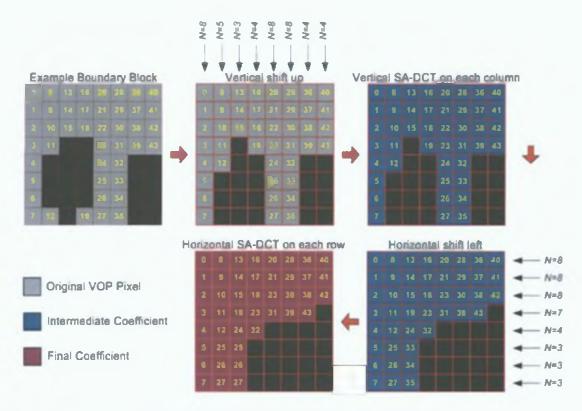

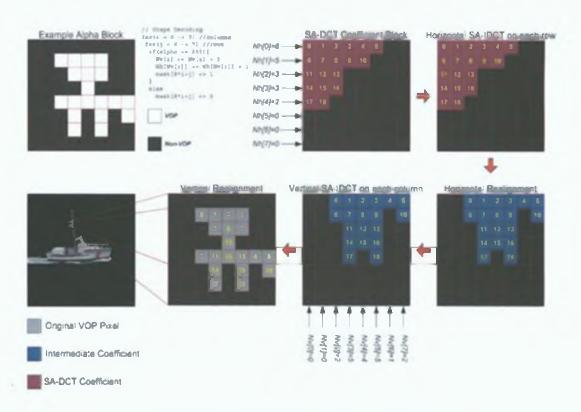

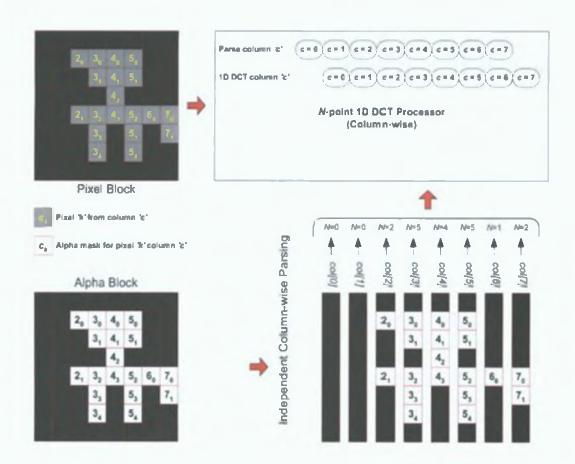

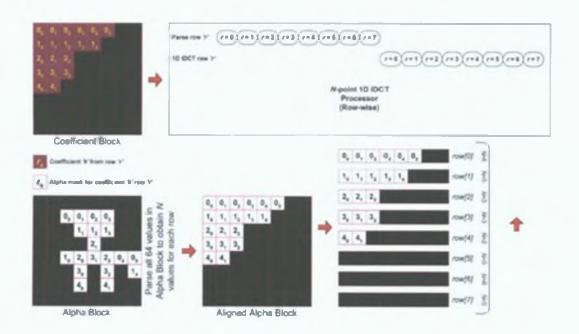

| 2 15 | The SA-DCT Algorithm Step-by-Step                                     | 33 |

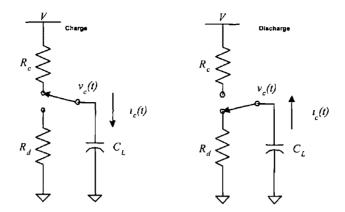

| 2 16 | Dynamic Charging and Discharging a Capacitive Load                    | 38 |

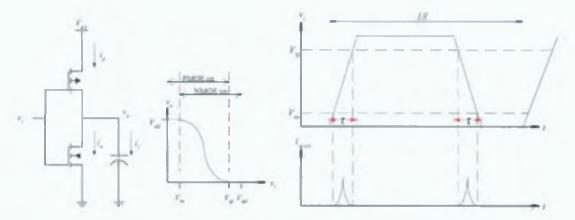

| 2 17 | CMOS Inverter Transfer Characteristic and Short-Circuit Current       | 39 |

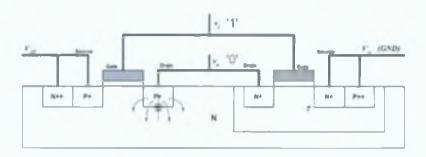

| 2 18 | Diode Leakage Current in a CMOS Inverter                              | 41 |

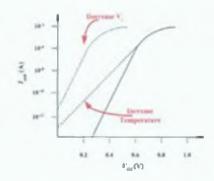

| 2 19 | Sub-threshold Current as a Function of Gate Voltage                   | 41 |

| 2 20 | Degenerated Voltage Level Driver                                      | 42 |

| 2 21 | A Pseudo-NMOS NOR Gate                                                | 42 |

| 2 22 | Static vs Dynamic Power                                               | 43 |

| 2 23 | Using Power [W] as a Design Metric                                    | 44 |

| 2 24 | Energy Delay Product (EDP) Solution Space                             | 45 |

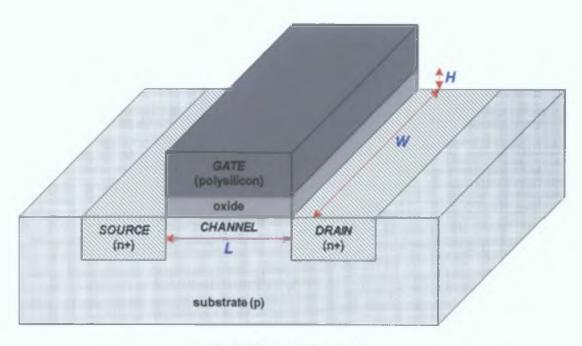

| 2 25 | NMOS Transistor                                                       | 50 |

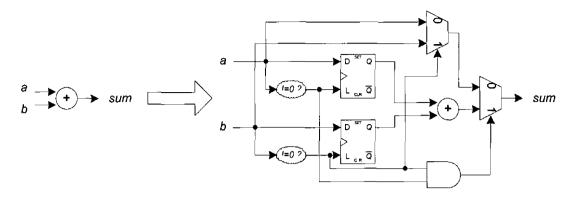

| 2 26 | Simple Multiply-Accumulate Circuit                                    | 54 |

| 2 27 | An Example of a Pipelined System                               | 58         |

|------|----------------------------------------------------------------|------------|

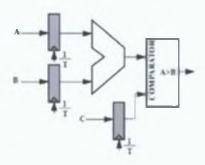

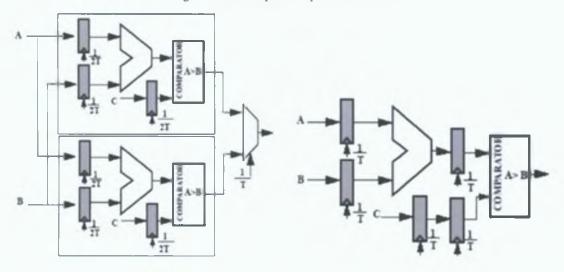

| 2 28 | Sample Comparator Circuit                                      | 59         |

| 2 29 | Sample Parallel Comparator                                     | 59         |

| 2 30 | Sample Pipelined Comparator                                    | 59         |

| 2 31 | Reducing Glitching by Balancing Signal Paths                   | 61         |

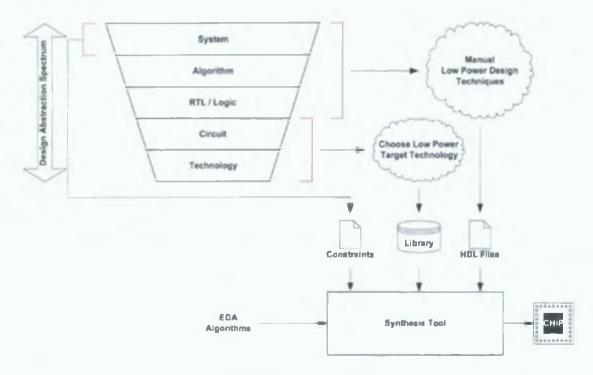

| 2 32 | Low Power Design Flow                                          | 64         |

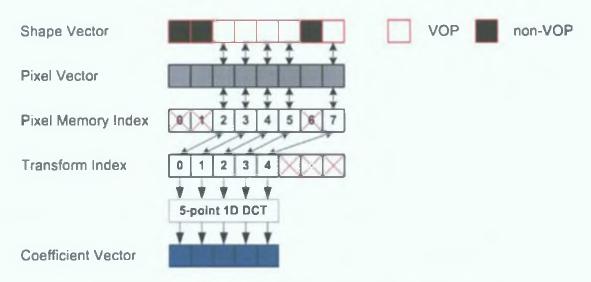

| 3 1  | The SA-DCT Algorithm Data Addressing                           | 70         |

| 3 2  | Mismatch Between Data Memory Index and Data Transform Index    | 71         |

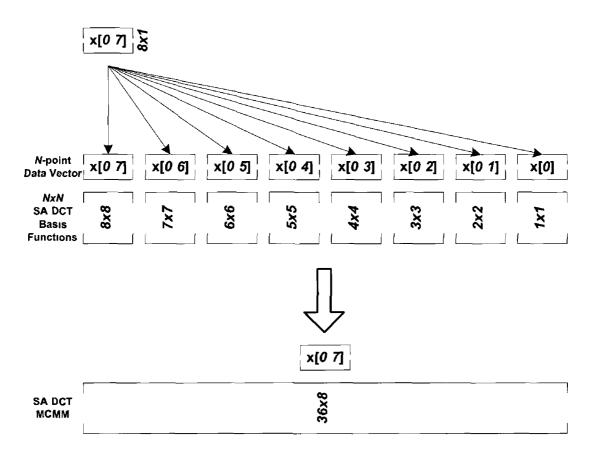

| 3 3  | The SA-DCT Basis Functions                                     | 72         |

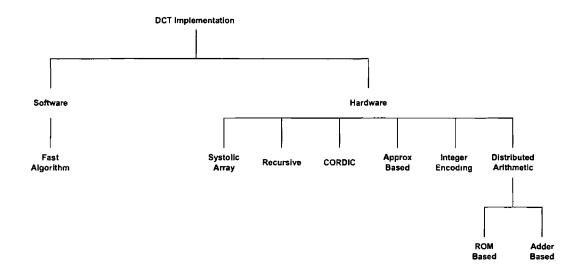

| 3 4  | Taxonomy of DCT Implementation Approaches                      | 74         |

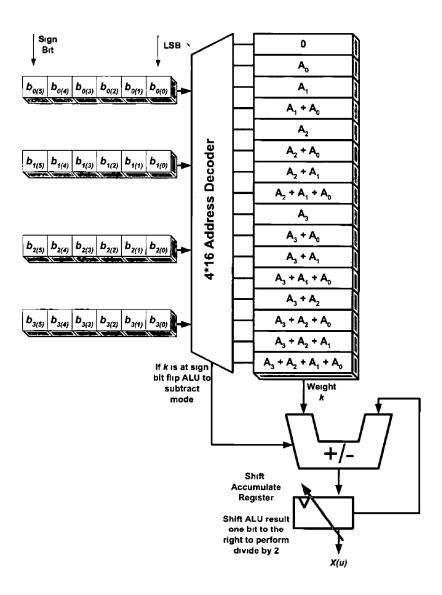

| 3 5  | Sample ROM-based DA Architecture                               | 79         |

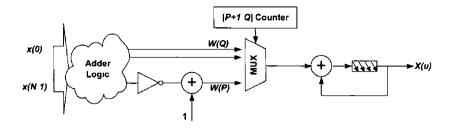

| 3 6  | Conceptual NEDA Architecture                                   | 81         |

| 3 7  | Recursive Architecture (Le et al)                              | 83         |

| 3 8  | Feed-Forward Architecture (Le et al)                           | 83         |

| 3 9  | Reconfigurable Processor Architecture (Tseng et al )           | 84         |

| 3 10 | Programmable Processor Architecture (Chen et al )              | 84         |

| 3 11 | Auto-Aligning Architecture (Lee et al.)                        | 85         |

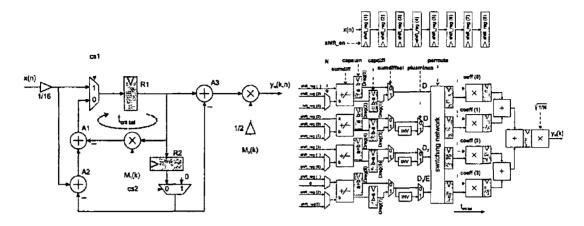

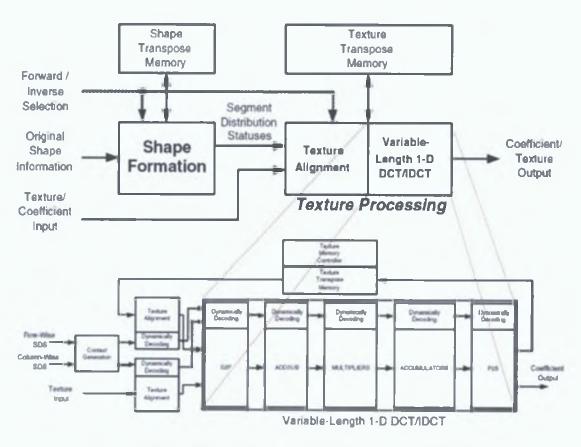

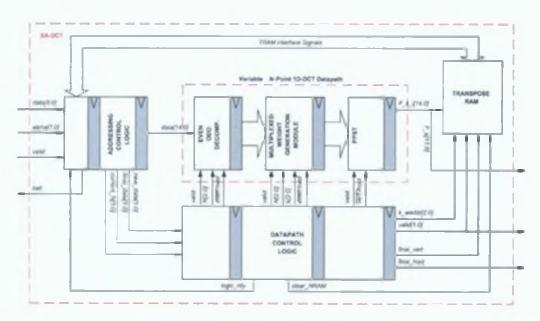

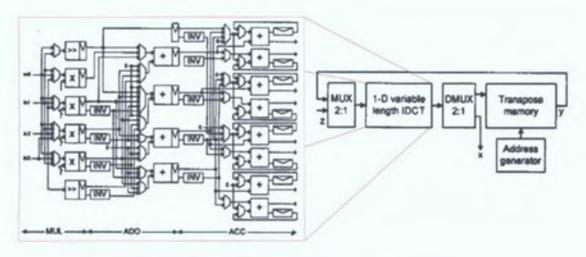

| 3 12 | Top-Level SA-DCT Architecture                                  | 87         |

| 3 13 | SA-DCT Vertical Raster Data Scanning                           | 87         |

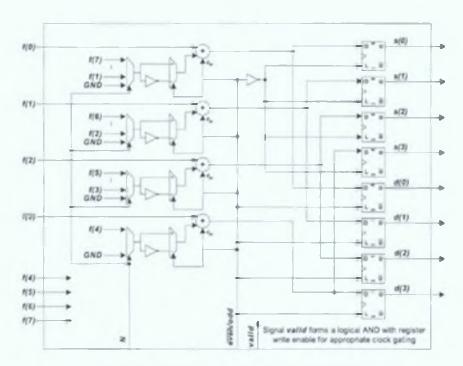

| 3 14 | Even-Odd Decomposition (EOD) Architecture                      | 90         |

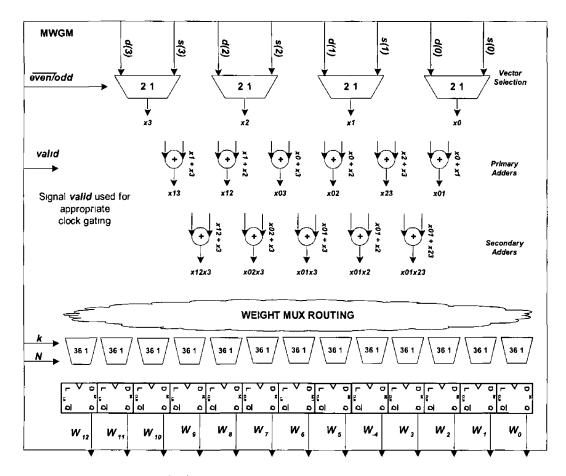

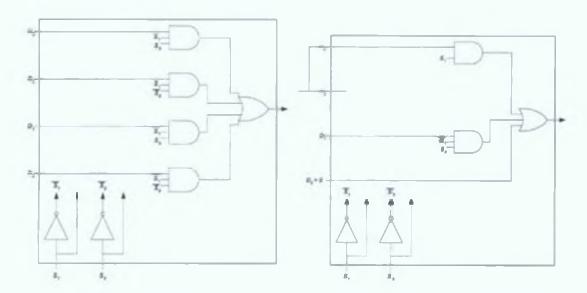

| 3 15 | Multiplexed Weight Generation Module (MWGM) Architecture       | 91         |

| 3 16 | Simple 4 1 MUX                                                 | 92         |

| 3 17 | Data Optimised 4 1 MUX                                         | 92         |

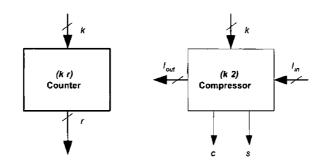

| 3 18 | General Counter and Compressor                                 | 93         |

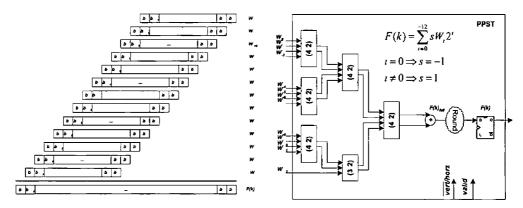

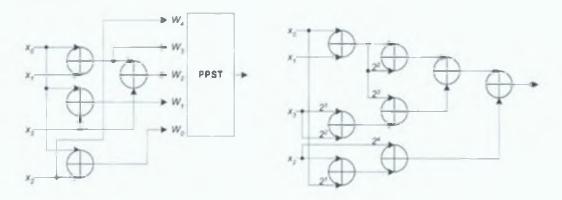

| 3 19 | Partial Product Summation Tree (PPST) Behavioural Architecture | 93         |

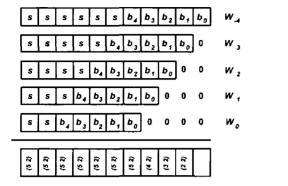

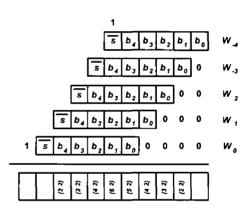

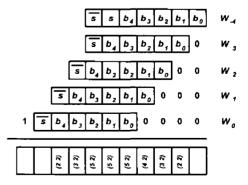

| 3 20 | Original Alignment of PPST Weights                             | 94         |

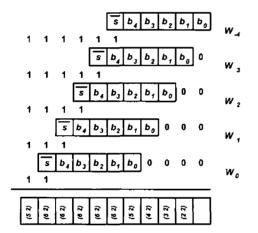

| 3 21 | First Sign Extension Exploit                                   | 94         |

| 3 22 | Reformulated PPST Weights                                      | 94         |

| 3 23 | Pre-addition of Constants                                      | 94         |

| 3 24 | Second Sign Extension Exploit                                  | 94         |

| 3 25 | Optimised PPST Logic                                           | 94         |

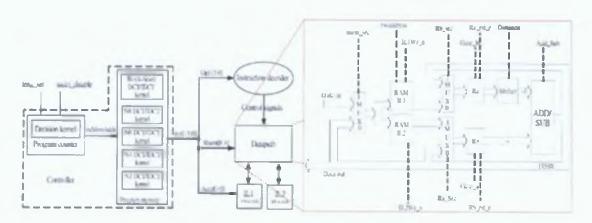

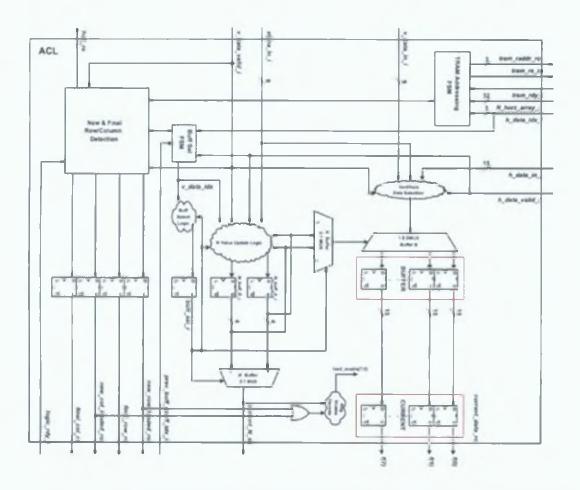

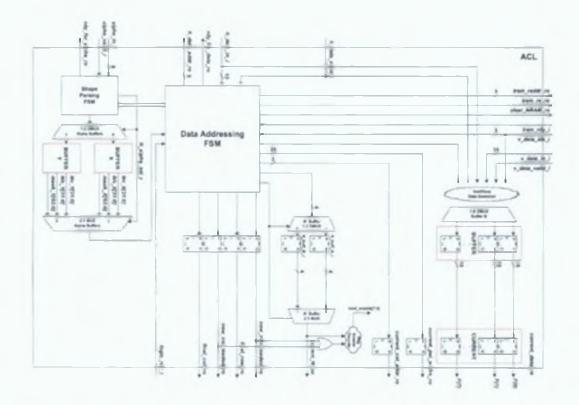

| 3 26 | Addressing & Control Logic (ACL) Architecture                  | 96         |

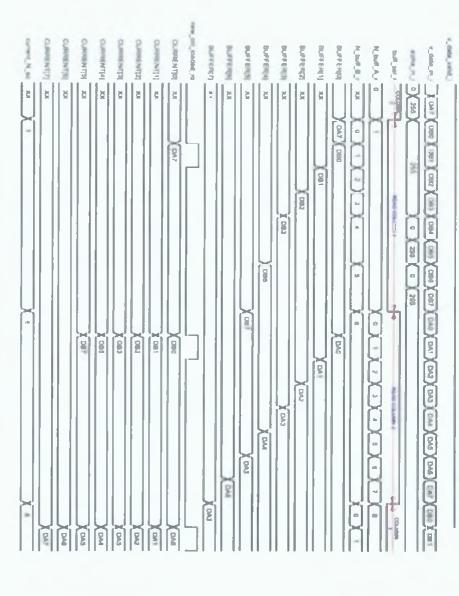

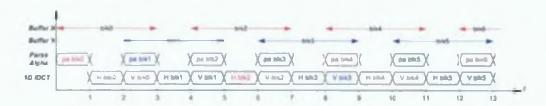

| 3 27 | Sample SA-DCT ACL Timing Diagram                               | 98         |

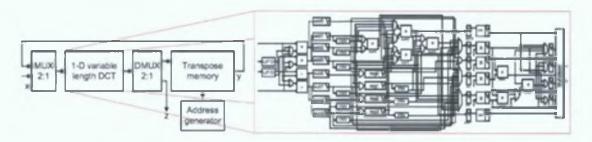

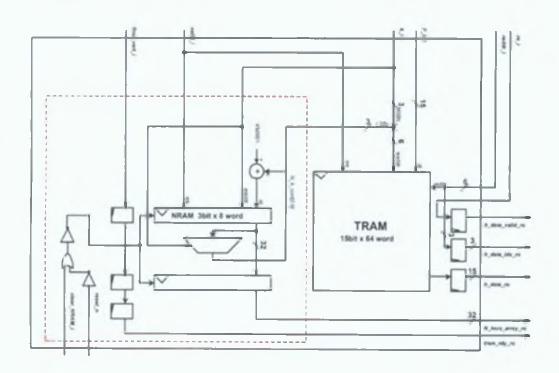

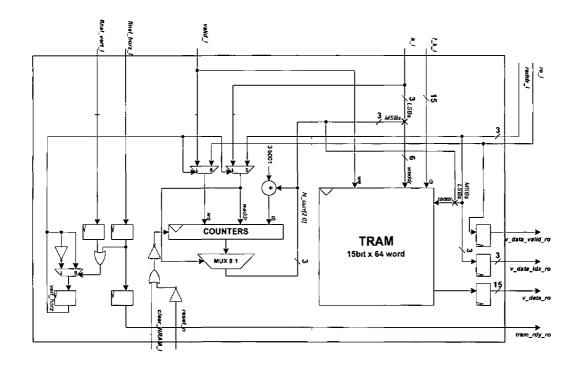

| 3 28 | TRAnspose Memory (TRAM) Architecture                           | 99         |

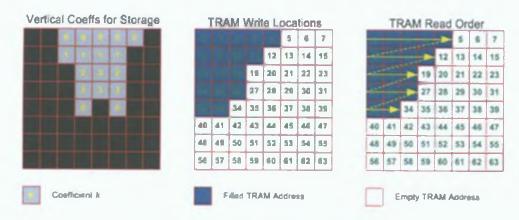

| 3 29 | Example SA-DCT TRAM Addressing                                 | 99         |

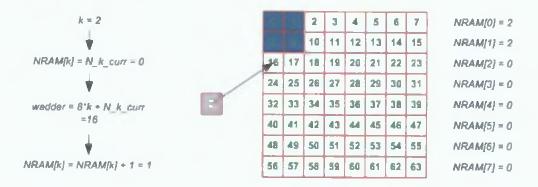

| 3 30 | Example SA-DCT TRAM Write                                      | <b>9</b> 9 |

| 3 31 | SA-DCT IP Core Verification Platform                           | 100        |

| 3 32 | Sample Object Reconstruction with $Q=-10$ and $T=11\ 0$        | 101        |

| 3 33 | Andy                                                           | 105        |

| 3 34 | Coastguard Object 1                                            | 105        |

| 3 35 | Container Object 1                                             | 105        |

| 3 36 | Hall Monitor Object 2                                                  | 105 |

|------|------------------------------------------------------------------------|-----|

| 3 37 | Sean                                                                   | 105 |

| 3 38 | Weather                                                                | 105 |

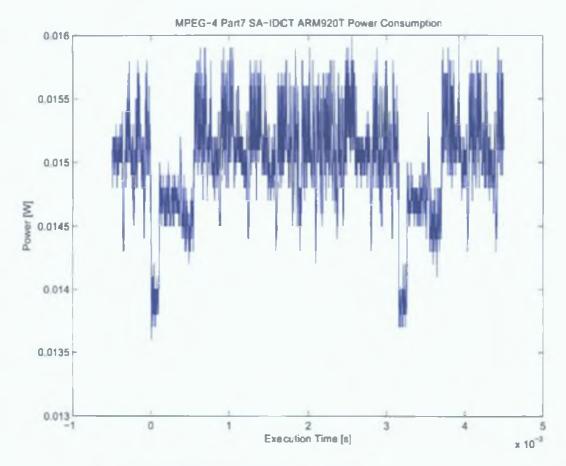

| 3 39 | MPEG-4 Part7 SA-DCT ARM920T Power Consumption                          | 107 |

| 3 40 | MPEG-4 Part 7 Fast SA-DCT Energy Characteristics on StrongARM SA-1100  | 108 |

| 3 41 | MPEG-4 Conformance Integration Hardware                                | 108 |

| 3 42 | ARM Virtual Socket Platform                                            | 111 |

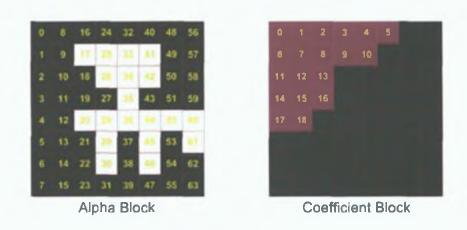

| 4 1  | The SA-IDCT Algorithm Data Addressing                                  | 115 |

| 4 2  | Sample SA-DCT Shape Parsing                                            | 116 |

| 4 3  | Sample SA-IDCT Shape Parsing                                           | 116 |

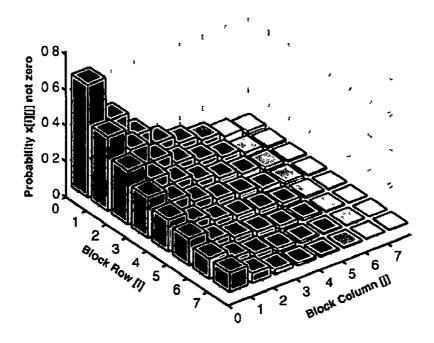

| 4 4  | Probabilities of Nonzero Occurrence for 8 × 8 DCT Coefficient Blocks   | 119 |

| 4 5  | Auto-Aligning Architecture (Hsu et al )                                | 121 |

| 4 6  | Top-Level SA-IDCT Architecture                                         | 123 |

| 47   | SA-IDCT Vertical Alpha Scanning and Horizontal Coefficient Scanning    | 123 |

| 48   | Even-Odd Recomposition (EOR) Architecture                              | 125 |

| 49   | SA-IDCT ACL Architecture                                               | 129 |

| 4 10 | SA-IDCT ACL Data Processing Pipeline                                   | 129 |

| 4 11 | SA-IDCT TRAM Architecture                                              | 131 |

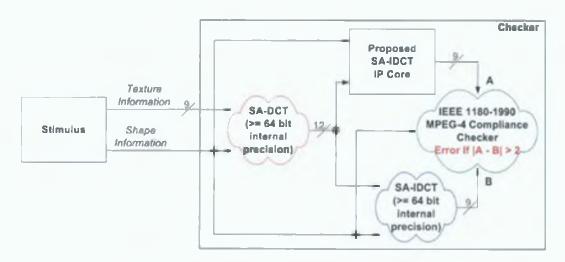

| 4 12 | SA-IDCT IP Core Verification Platform                                  | 132 |

| 4 13 | Andy                                                                   | 136 |

| 4 14 | Coastguard Object 1                                                    | 136 |

| 4 15 | Container Object 1                                                     | 136 |

| 4 16 | Hall Monitor Object 2                                                  | 136 |

| 4 17 | Sean                                                                   | 136 |

| 4 18 | Weather                                                                | 136 |

| 4 19 | MPEG-4 Part7 SA-IDCT ARM920T Power Consumption                         | 138 |

| 4 20 | MPEG-4 Part 7 Fast SA-IDCT Energy Characteristics on StrongARM SA-1100 | 139 |

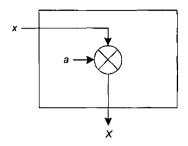

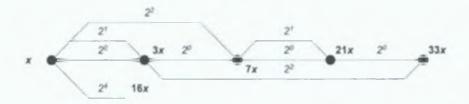

| 5 1  | Single Constant Multiplier Behavioural Architecture                    | 145 |

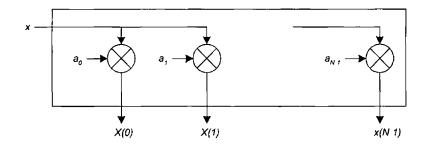

| 5 2  | Constant Multiplier Block Behavioural Architecture                     | 146 |

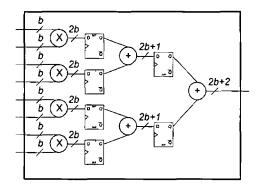

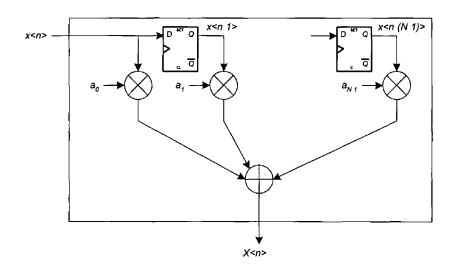

| 5 3  | FIR Filter Behavioural Architecture                                    | 146 |

| 5 4  | FIR Sub-Expression Selection Example                                   | 148 |

| 5 5  | Example FIR Architecture Using Sub-Expressions                         | 148 |

| 5 6  | Simple FIR Sub-Expression Selection Options                            | 148 |

| 5 7  | Simple FIR Sub-Expression Selection Options                            | 149 |

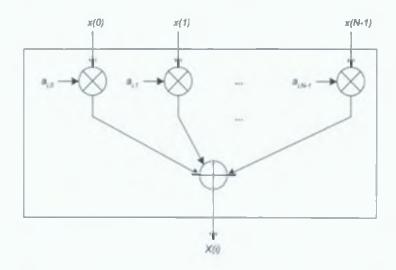

| 5 8  | Dot Product Behavioural Architecture                                   | 150 |

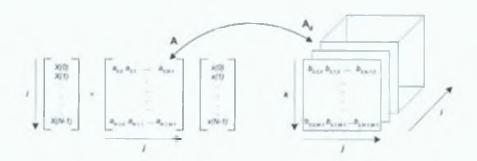

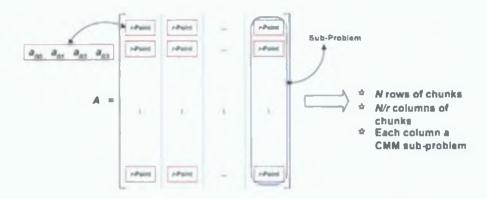

| 59   | CMM Distributed Signed Digit 3D Matrix                                 | 150 |

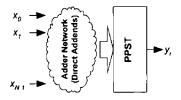

| 5 10 | P1D Architecture                                                       | 152 |

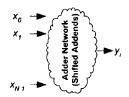

| 5 11 | P2D Architecture                                                       | 152 |

| 5 12 | CMML Divide and Conquer                                                | 153 |

| 5 13 | Sample Acyclic Graph of a Constant Multiplier Block                    | 154 |

| 5 14 | Sample PID Architecture                                                | 160 |

| 5 15       | Sample P2D Architecture                                | 160 |

|------------|--------------------------------------------------------|-----|

| 5 16       | Summary of the CMM Algorithm                           | 163 |

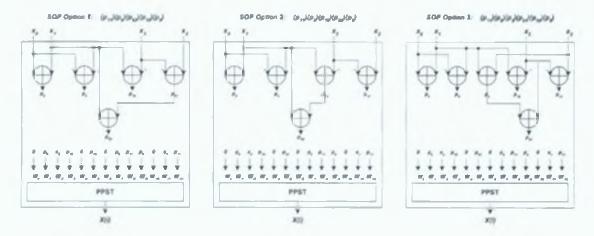

| 5 17       | Architecture Options Implied by Example SOP            | 168 |

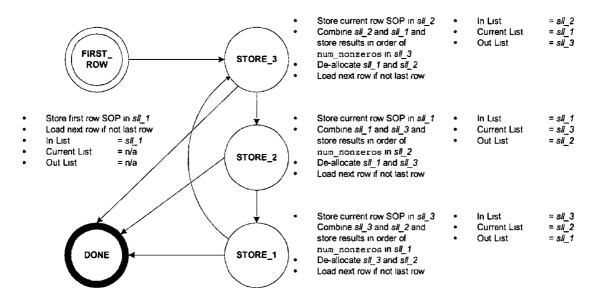

| 5 18       | Permutation SOP Building Finite State Machine          | 169 |

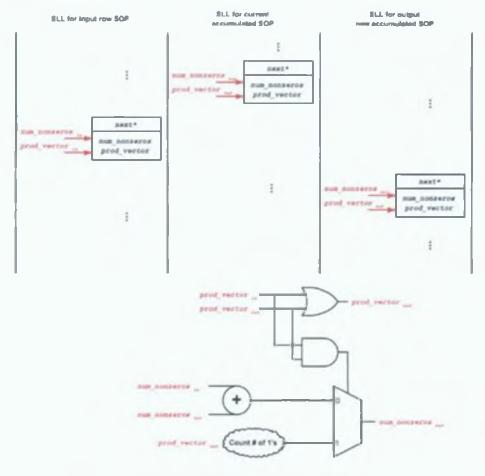

| 5 19       | Node Combination at DPL                                | 170 |

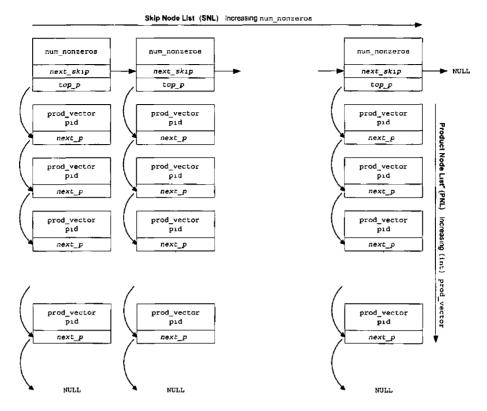

| 5 20       | DPL Unique Implementation Skip List                    | 172 |

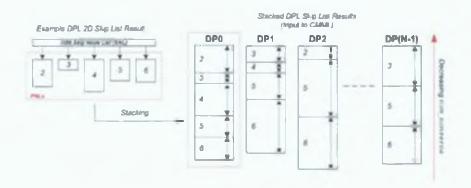

| 5 21       | DPL Result Stacking Prior to CMML Processing           | 177 |

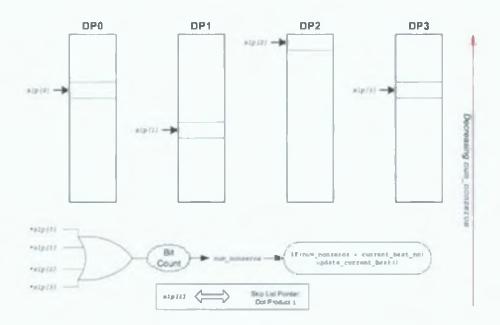

| 5 22       | CMML Processing                                        | 177 |

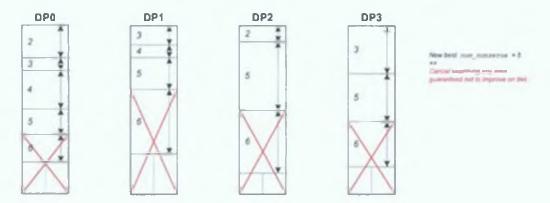

| 5 23       | Example CMML Search Space Reduction                    | 178 |

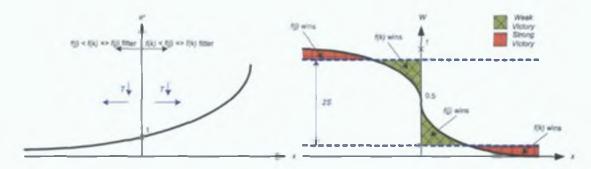

| 5 24       | Boltzmann Decision Based Simulated Annealing           | 182 |

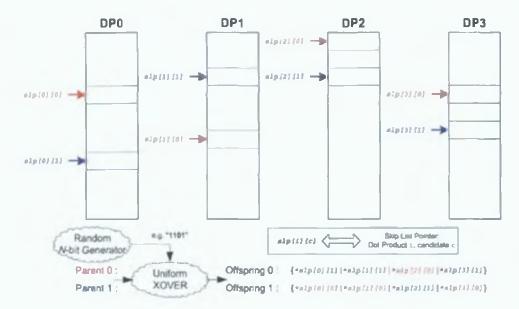

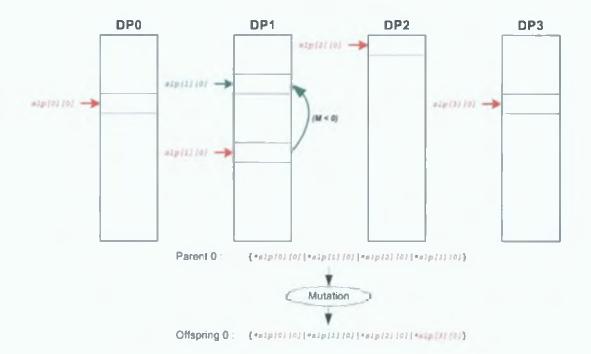

| 5 25       | Uniform Crossover Example                              | 184 |

| 5 26       | Mutation Example                                       | 185 |

| 5 27       | Binomial Distribution Function                         | 186 |

| 5 28       | Re-Aligned Distribution                                | 186 |

| 5 29       | SA-DCT as an MCMM Problem                              | 189 |

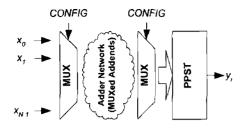

| 5 30       | Time-MUX Addends & PPST                                | 190 |

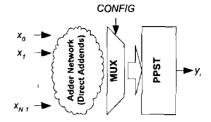

| 5 31       | Time-MUX PPST                                          | 190 |

| 6 1        | Regular Adder and Guarded Evaluation Adder             | 201 |

| 62         | Sample Images Captured by the Philips FluidFocus Lens  | 204 |

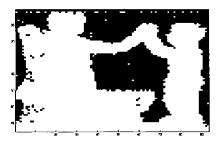

| 63         | Near Focused Image                                     | 205 |

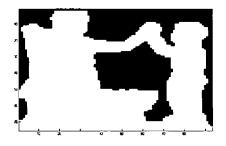

| 64         | Far Focused Image                                      | 205 |

| 6 5        | Rough Foreground Mask                                  | 206 |

| 66         | Post-Processed Foreground Mask                         | 206 |

| 67         | Segmented Foreground Object                            | 206 |

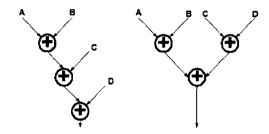

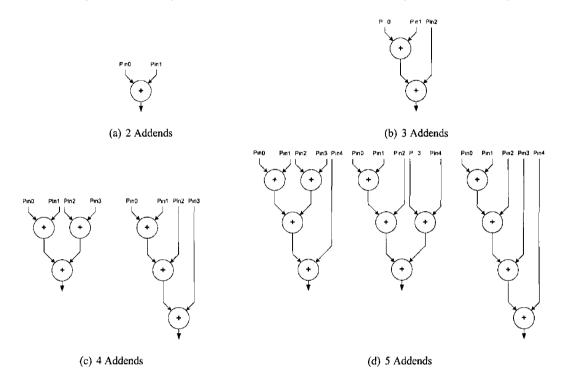

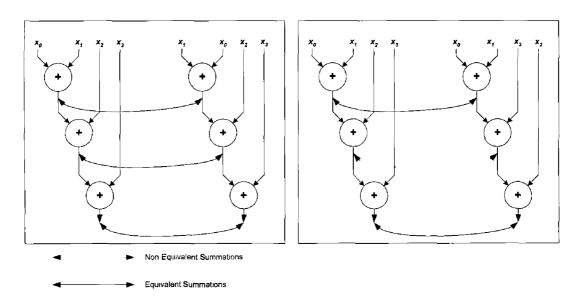

| <b>A</b> 1 | Multi-Operand Addition                                 | 209 |

| A 2        | Adder Topology Options for Different Number of Addends | 210 |

| A 3        | Hardware Associativity and Commutativity Examples      | 211 |

# LIST OF TABLES

| 2 1        | Weighting Factors for $K=4$ on the StrongARM Processor                   | 47  |

|------------|--------------------------------------------------------------------------|-----|

| 3 1        | SA-DCT N-point Data Decomposition                                        | 89  |

| 3 2        | Total Number of Unique Possibilities for Each Distributed SA-DCT Weight  | 92  |

| 3 3        | SA-DCT Core IEEE 1180-1990 Results for $Q = -12$ , $f = 4$               | 101 |

| 3 4        | SA-DCT 90nm TSMC Synthesis Results and Benchmarking                      | 102 |

| 3 <b>5</b> | Available MPEG-4 Standard Test Sequences                                 | 104 |

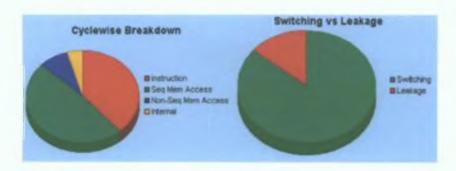

| 3 6        | SA-DCT 90nm TSMC Power Consumption                                       | 104 |

| 3 7        | Normalised SA-DCT Power and Energy Benchmarking                          | 106 |

| 3 8        | Software SA-DCT StrongARM SA-1100 Energy Statistics                      | 107 |

| 3 9        | Normalised Power and Energy Benchmarking Against Software SA-DCT         | 108 |

| 3 10       | SA-DCT FPGA Synthesis Results                                            | 110 |

| 4 1        | Total Number of Unique Possibilities for Each Distributed SA-IDCT Weight | 125 |

| 4 2        | SA-IDCT EOR Ping Pong Data Ordering                                      | 128 |

| 4 3        | SA-IDCT Core IEEE 1180-1990 Results for $Q = -12$ , $f = 4$              | 132 |

| 44         | SA-IDCT 90nm TSMC Synthesis Results and Benchmarking                     | 133 |

| 4 5        | SA-IDCT 90nm TSMC Power Consumption                                      | 135 |

| 4 6        | Normalised SA-IDCT Power and Energy Benchmarking                         | 137 |

| 4 7        | Software SA-IDCT StrongARM SA-1100 Energy Statistics                     | 138 |

| 4 8        | Normalised Power and Energy Benchmarking Against Software SA-IDCT        | 139 |

| 4 9        | SA-IDCT FPGA Synthesis Results                                           | 141 |

| 5 1        | 16-bit Daubechies D4 Full Adder Requirements                             | 176 |

| 5 2        | CMML Genetic Algorithm Parameters                                        | 186 |

| 5 3        | 1D 8-point DCT/IDCT Adder Unit / Full Adder Requirements                 | 187 |

| 5 4        | Operating Conditions of Proposed CMM Optimisation Algorithm Test Cases   | 187 |

| A 1        | Topology 1 Options                                                       | 211 |

| A 2        | Topology 2 Options                                                       | 211 |

| <b>A</b> 3 | Unique Adder Permutations    | 212 |

|------------|------------------------------|-----|

| A 4        | The First 32 Values of $T_n$ | 218 |

| A 5        | The First 32 Values of $P_n$ | 220 |

N O'Connor, V Muresan, A Kınane, D Larkın, S Marlow, and N Murphy, *Hardware Acceleration Architectures for MPEG-based Mobile Video Platforms A Brief Overview*, in Proc. 4th European Workshop on Image Analysis for Multimedia Interactive Services (WIAMIS), London, April 9–11, 2003, pp 456-461

A Kinane, V Muresan, N O'Connor, N Murphy, and S Marlow, *Energy-Efficient Hardware Architecture for Variable N-point 1D DCT*, in Proc International Workshop on Power and Timing Modelling, Optimization and Simulation (PATMOS), Santorini, Greece, September 15-17, 2004, pp. 780-788

A Kinane, V Muresan, and N O'Connor, *An Optimal Adder-Based Hardware Architecture for the DCT/SA-DCT*, m Proc SPIE Video Communications and Image Processing (VCIP), Beijing, China, July 12-15, 2005, pp 1414–1417

D Larkin, A Kinane, V Muresan, and N O'Connor, *Efficient Hardware Architectures for MPEG-4 Core Profile*, in Proc 9th Irish Machine Vision and Image Processing Conference (IMVIP), Belfast, Northern Ireland, August 30-31, 2005, pp 249–252

A Kinane, A Casey, V Muresan, and N O'Connor, FPGA-Based Conformance Testing and System Prototyping of an MPEG-4 SA-DCT Hardware Accelerator, in Proc IEEE International Conference on Field Programmable Technology (FPT), Singapore, December 11-14, 2005, pp 317-318

A Kinane, V Muresan, and N O'Connor, *Optimisation of Constant Matrix Multiplication Operation Hardware Using a Genetic Algorithm*, in Proc 3rd European Workshop on Evolutionary Computation in Hardware Optimisation (EvoHOT), Budapest, Hungary, April 10-12, 2006

A Kinane, V Muresan, and N O'Connor, Towards an Optimised VLSI Design Algorithm for the Constant Matrix Multiplication Problem, in Proc. IEEE International Symposium on Circuits and System (ISCAS), Kos, Greece, May 21-24, 2006

D Larkin, A Kinane, V Muresan, and N O'Connor, *An Efficient Hardware Architecture for A Neural Network Activation Function Generator*, in Proc International Symposium on Neural Networks (ISNN), Chengdu, China, May 29-31, 2006

A Kinane and N O'Connor, An Adder Based Hardware Architecture for the MPEG-4 Shape Adaptive IDCT, in Proc IEE Irish Signals and Systems Conference (ISSC), Dublin, Ireland, 28-30 June 2006

| CHAPTER 1 | <br> |               |

|-----------|------|---------------|

| }         |      |               |

|           |      |               |

|           |      | _Introduction |

# 11 The Emergence of Mobile Multimedia

Communication is arguably the most fundamental facet of human behaviour. We experience audiovisual interactions daily and they occur in all areas of our lives. Considering that this is true for people of every race, age, profession and any other qualifier one can imagine, it is easy to see why there is such a continual demand for more sophisticated communication systems. The medium used for communication has evolved with this demand due to the astonishing advancements in the electronics industry and telecommunications infrastructure over the past fifty years [1, 2, 3, 4]. For example, the mobile phone has permeated our society to the extent that it is now an essential device for daily living. According to American research firm IDC, the number of mobile phone users approached 1.4 billion in 2004 [5]. Developments have not been restricted to the audio domain, there have also been advances in the visual domain in areas such as video telephony, video conferencing as well as the development of interactive digital television [6, 7]. The most recent trend has seen audio-visual communication systems shift to mobile platforms. Indeed mobile devices are serving as a point of convergence for communication, internet and personal computing applications yielding a truly ubiquitous multi-purpose mobile computing device [8, 9].

# 12 Grand Challenges Facing Mobile Computing

The emergence of the convergent mobile device poses huge technical challenges especially when end users demand increasingly complex content-based interactive services on such a small piece of hardware. The challenges involved can be broadly categorised into three problems, application development, content delivery and content processing. This section briefly outlines these challenges to give context for the research undertaken in this thesis. A more technical overview and discussion of these issues is given in Chapter 2.

# 1.2.1 Application Development Challenges

The modern mobile phones now available offer many more applications than its name implies – it is no longer merely a device for making voice calls. There is a multitude of applications emerging that include: personal organiser, e-mail, mobile internet, MP3 audio codec, digital camera, video telephony, mini-camcorder, mobile gaming, mobile TV, digital radio... and the list is ever increasing! An example of such a device is the new Nokia 7710 that offers many of these features [10]. We are witnessing the emergence of a ubiquitous personal gadget that covers the entire spectrum of daily activities and their associated data [11, 12]. As such, it represents a mass market product that is an ideal technical platform for cutting edge research.

### 1.2.1.1 Mobile Computing Market Demographics

Although technophiles will always provide a market for multi-purpose gadgets, it remains to be seen whether such a convergent device will be considered necessary by the wider population, especially by people who are not technically minded. Sceptics worry about possible market disinterest due to feature overload [13]. However it is short-sighted to predict that just because there may be no perceived widespread demand for a convergent device at present, there will be no such demand in the future. To illustrate how a market can boom so quickly consider that in 1999, 12.8% of US internet users had at least one MP3 music file on their hard disks [9]. Since then, the adoption of digital audio jukebox products such as the Apple iPod has mushroomed. It is estimated that shipments of MP3 players rose by 116% in 2004 and that the total number of shipments is estimated to rise by a factor of four by 2009 [14]. Now consider that in 2004, 13% of US internet users had at least one video file (>150MB) on their hard disks. It is reasonable to assume that there will be a similar growth in the mobile video market, considering how quickly digital cameras have become almost a standard feature in new mobile phones. Evidence of this emerging trend is clear given that Apple have recently released their fifth generation iPod, which is capable of video playback and can store up to 150 hours of video content [15].

To guarantee the widespread adoption of the convergent device, any proposed applications must be easy to use and be of comparable performance and quality to their desktop equivalent (albeit allowing for the device limitations as discussed in Section 1.2.3). One only has to consider the failure of the initial Wireless Application Protocol (WAP) service compared to the facile nature of web surfing on a desktop to see how easily the consumer can be turned off by poor application usability and quality [16]. The work in this thesis is primarily concerned with digital image and video applications on a mobile device, and for such applications to be successful the user must feel satisfied with the same usability and quality criteria. The rapid advancement of digital cameras integrated in mobile phones implies that users demand quality if they are to abandon their dedicated camera devices and trust their convergent device for quality photo capture. Samsung aim to push toward the 5-Mexapixel camera phone leaving dedicated digital still cameras as devices only used by professional photographers [13]. For digital video on a mobile device to be successful, there is a need for better network infrastructure (see Section 1.2.2) and improved video compression. Video data requires compression when you consider that the bit rate for uncompressed Common Interchange Format (CIF) resolution video is approximately 4.5MB/s (see Chapter 2 for details). High compression ratios and low bit rate coding is especially necessary in the mobile domain where there is relatively low bandwidth.

#### 1212 MPEG-4 - Low Bit-rate Mobile Video Telephony

The emerging industry compression standard for low bit-rate video applications is MPEG-4 [17]. A comprehensive survey of video compression standards and techniques is given in Chapter 2. One of the essential advances achieved by MPEG-4 is that it considers a scene as being composed of distinct audio-visual objects and each is coded independently [18, 19]. This is revolutionary, particularly in terms of how the video data is coded as explained in detail in Chapter 2. One can imagine in a mobile video telephony application that only encoding and transmitting the object of interest (e.g. the human face) while ignoring the background is very bandwidth efficient (and thus the service is cheaper). This additional compression unfortunately comes at the cost of increased computational complexity, and this is particularly troublesome given mobile device limitations (see Section 1.2.3). One of the most computationally demanding algorithms at the heart of the MPEG-4 object-based compression scheme is the Shape Adaptive Discrete Cosine Transform (SA-DCT) and its inverse the SA-IDCT [20, 21]. When aiming to achieve real time video applications on mobile devices, the computational burden of the associated algorithms is a primary obstacle—especially given that the platform has limited processing capability and is battery powered. Efficient hardware acceleration implementations of the SA-DCT and SA-IDCT suitable for a mobile device are thus key requirements and are the topics of Chapters 3 and 4

A key point to note is that an MPEG-4 codec is not technically orthogonal to the other applications emerging for the mobile device (e.g. gaming, mobile TV, etc.) The envisaged applications can be considered to be built using a set of lower-level basic video processing blocks that may be termed basic enabling technologies. The SA-DCT/IDCT is an example of one such basic enabling technology. The SA-DCT block is used in an MPEG-4 application, but may also be used to estimate image regions of high spatial frequency to aid object-segmentation (i.e. breaking the image up into semantic regions) in a content management or security application. Similarly specific image filters can be implemented for visual quality enhancement of highly compressed video, but again suitably configured can be used for spatial segmentation, or for identifying moving objects when used in conjunction with the results of a motion estimator. Since basic enabling technologies such as the SA-DCT have great potential for re-use across many mobile applications, efficient implementation of such technologies is critical to the successful development of the convergent device.

There will always be a demand by end users for more advanced features and functionality. Users demand multi-feature integration on a reasonably small mobile platform with improved battery life. As discussed in Section 1.2.3, these are conflicting demands as far as a design engineer is concerned and as such, research in the area of mobile multimedia applications and devices is a very active field.

#### 1 2 2 Networking and Communication Challenges

Mobile networks have developed significantly in recent years and more and more applications are shifting to the mobile domain. Second generation mobile devices (2G) use Global System for Mobile Communication (GSM) technology, which in its basic form offers 9 6 kb/s. Third generation (3G) networks use the Universal Mobile Telecommunications System (UMTS) which offers more than 2 Mb/s and it is estimated that 48 million 3G handsets were shipped in 2004 [5]. Most mobile communication systems around the world at the moment use 2G technology but 3G is becoming widespread. Despite the growth of data rates in mobile networks, bandwidth is still a valuable commodity, especially if the data being

carried over these networks is audio-visual data [22].

There are other network design challenges in addition to the need for higher bandwidth [23]. For "anytime anywhere" computing, next generation networks should support ubiquitous intelligent connectivity. Users need to be able to roam seamlessly between networks without needing detailed (or ideally any) knowledge at the technology level. Each device should be uniquely addressable regardless of global location – fusing the conventional idea of a telephone number and a computer internet MAC address (note IPv6 will enable this [23]). The convergent device should provide personalised content and be location aware. One could envisage a scenario that a user is abroad and the device lists nearby restaurants that serve his/her favourite dishes. Global Positioning System (GPS) technology is already appearing in consumer electronic devices and its evolution is key to the enabling of personalised, location aware technology. Next generation networks need to be robust and reliable as well as delivering excellent quality of service. The user needs assurance of privacy and security if the device is being used with sensitive data, e.g. in a mobile banking application. Clearly there are challenges facing the networking and communications community to provide the backbone that will support the envisaged convergent device. Although not tackled directly in this work, progress in this field is essential to the success of ubiquitous mobile computing.

## 1.2.3 Hardware Device Design Challenges

The applications conceived for the convergent device as outlined in Section 1.2.1 are sometimes more artistically referred to as "e-Dreams" – the concept whereby the world starts to adapt to the wishes of the consumer wherever he/she may be [24]. This requires the convergence of computing technology, wired wireless connectivity, non-keyboard user interfaces and distributed transducer networks. However, the technology push for these e-Dreams ("7th heaven of software") leads to relentless CMOS scaling and the "nano-scale hell of physics" [25]. These are two paradigms that on the one hand enable each other, but on the other hand the conceptual gap between them is diverging at a Moore type rate. The e-Dream creators expect increased reliability, security, adaptivity, interoperability, battery life and so on but hardware engineers must struggle with the practical energy-flexibility-cost issues associated with deep-submicron design.

# 1.2.3.1 Limited Interfaces

There are many technical obstacles to implementing the "digital dream" applications that are currently evolving [25]. The convergent mobile device has some obvious limitations compared to a desktop platform e.g. limited display size, limited input capability [22]. As feature integration continues to increase, designers are facing aggressive miniaturisation requirements and the permissible footprint of each component (both software and hardware based) is very restricted if the device is to be as small and portable as possible.

## 1.2.3.2 Limited Processing Capability

Mobile embedded systems have limited processing power compared to a desktop. It is not feasible to use a large multi-GHz Complex Instruction Set Computer (CISC)-based processor such as the Intel Pentium4 [26] which would need a bulky cooling fan subsystem. Embedded systems tend to use Reduced

Instruction Set Computer (RISC) such as those designed by companies such as ARM and MIPS [27, 28] Operating frequencies of such processors tend to be in the order of hundreds of MHz (e.g. ARM920T processor can run up to 250MHz [29]). While it must be said that it is naive to compare processors based solely on operating frequency [27] (memory access time, instruction set parallelism etc. should all be considered), it is safe to claim that embedded processors have less "horsepower" compared to their desktop counterparts. As such, computationally demanding multimedia applications with heavy data throughput requirements pose a big problem in the mobile domain. Coupled with this issue, embedded systems also have a reduced memory capacity (both RAM and HDD) compared to desktops (RAM > 1GB and HDD > 100GB). For example the new Nokia 7710 has only 90MB of RAM and a maximum of 512MB of flash memory for storage [10]. Progress in the field of embedded memories and mobile hard disk drives is ongoing [30] and the Samsung SGH-1300 released in early 2005 comes with a 3GB HDD

## 1233 Limited Battery Life

Perhaps the most pressing challenge facing mobile system designers is that of limited battery energy and short battery life. In VLSI engineering, the trade off between high speed and minimum area has traditionally been the most dominating design constraint. Power consumption issues were usually a mere afterthought and any power savings gained were considered a bonus. More recently, power has become the high priority constraint due to the ongoing trend that has seen a shift to battery operated wireless platforms for multimedia applications [31, 32, 33]. The ever-increasing device capability coupled with unrelenting miniaturisation trends has had an enormous impact on circuit power consumption and requires serious consideration [34]. It is now crucial for designers to tackle this issue at every stage in the design process and at all levels of abstraction to make "digital dreams" a reality.

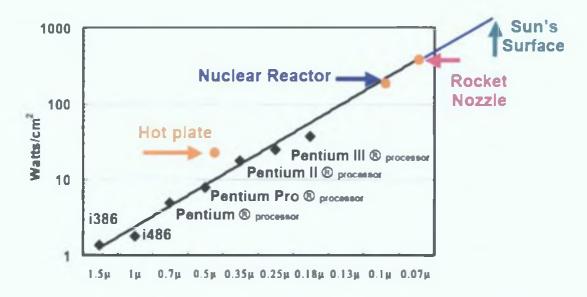

Technology scaling is improving continuously and showing no immediate signs of reaching fundamental limits [35]. Such improvements mean packing more functionality into a smaller area [33]. Unfortunately however, scaling causes increased power density as demonstrated in Figure 1.1 and this is a problem, particularly in a wireless application where cooling fans and subsystems are not feasible [36]. As this graph shows, the constraint for producing smaller devices in the future is not necessarily manufacturability but power consumption.

The requirement for advanced functionality coupled with portability means more power hungry computation and bigger, bulkier batteries. Batteries are usually the most dominant component of a mobile device in terms of its weight. There are two complementary ways to approach the problem of power constraints. One obvious way involves developing better battery technology since conventional nickel-cadmium batteries only provide 20Wh per pound of weight [34]. Although advances in battery technology are being made (as discussed in Chapter 2), progress is relatively slow compared to advances in technology scaling and wireless application development. Thus, in tandem with developing better batteries, hardware engineers should give prime importance to designing circuits that are as energy efficient as possible since the total battery energy is finite. Energy efficiency is critical if the intended application is as demanding as real time wireless MPEG-4 decoding and there is a constraint on the size of battery being used. Battery life has become a prime product differentiator and this has led to wide research in the field of low power design.

Figure 1.1: Power Density of Silicon Versus Process Technology According to Intel [33]

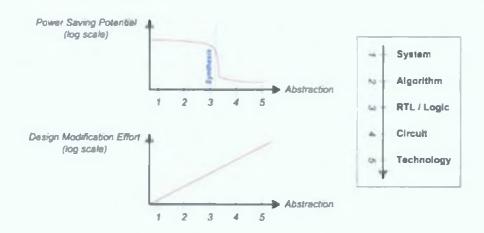

Figure 1.2: Power Savings at Various Levels of Design Abstraction

## 1.2.3.4 Power - A Primary Design Constraint

Chapter 2 focuses in detail on why power has become a primary design constraint. The sources of power consumption in an integrated circuit are elaborated, and the common techniques used to reduce this dissipation are detailed. The overriding theme is that most potential energy savings exist at the higher levels of abstraction (as illustrated in Figure 1.2), since there exists greater degrees of design freedom [37]. This is the motivating argument for focusing on system/algorithmic level optimisations as opposed to technology/layout/circuit level tweaks when designing the SA-DCT and SA-IDCT implementations proposed in Chapters 3 and 4.

Digital video processing and compression involves a lot of complex digital signal processing (DSP). As discussed in more detail in Chapter 2, the central processor (e.g. ARM RISC) in an embedded system is invariably relieved of the most computationally demanding DSP tasks by implementing some parallel co-processor or dedicated hardware accelerator [38, 21]. As mentioned previously, silicon real estate on

the convergent device is limited so the overhead of any extra logic should be worthwhile in the sense that this extra hardware should ideally be flexible enough to be re-usable for different applications and is thus not sitting idle for long periods of time. This hardware flexibility is a key concern, especially given the range of applications being constantly dreamt up.

#### 1.2.4 Motivation for Thesis

The grand challenges facing mobile computing mean that there is huge scope for research in this domain. The work in this thesis is focused on two of the basic enabling technologies that support mobile video applications, namely the SA-DCT and the SA-IDCT. It should be noted that both of these technologies are instances of a more general computation – both are constant matrix multiplication operations. Thus, this thesis also proposes an algorithm for the efficient hardware design of any general constant matrix multiplication equation. This algorithm can be used to design efficient hardware for a wide variety of signal processing basic enabling technologies that are needed on a convergent mobile device.

#### 1.2.4.1 Power Efficient Hardware for SA-DCT/IDCT

As mentioned in Section 1.2.1, the SA-DCT and SA-IDCT have re-use potential since they may be leveraged in various video processing applications. As such, they are valid candidates for implementation as hardware accelerated cores designed with power as a primary design constraint. It is proposed that power should be on an equal footing with the traditional constraints of speed and area. Much of the prior art in terms of hardware to implement the SA-DCT/IDCT does not address all of the required processing steps, and indeed none of the identified techniques are designed with power as a primary design constraint. With a mobile platform in mind, the latter is very important and the SA-DCT/IDCT architectures proposed in Chapters 3 and 4 aim to fill this void.

# 1.2.4.2 Efficient Hardware Resource Allocation for Constant Matrix Multiplication Operations

From a more general viewpoint, many of the DSP basic enabling technologies (e.g. SA-DCT/IDCT) are dominated by the so-called "fundamental" operations of multiplication and addition [39]. More specifically, they contain many instances of "multiplication by constants" (i.e. in the product  $a \times x$  when the multiplier a is a constant and the multiplicand x is a variable). Research has shown that for a survey of more than two hundred industrial examples, over 60% have greater than 20% operations that are multiplications with constants [40]. Apart from the DCT/SA-DCT, some other common enabling technologies that use multiplication by constants include digital filters (both FIR and IIR), the Discrete Fourier Transform (DFT), colour space conversion transforms, and the Discrete Wavelet Transform (DWT) to name but a few [41]. Optimisation of these kind of multiplications will significantly impact the performance of such tasks and the global system that leverages them. Since multiplication by constant operations are widespread in DSP applications, there has been widespread research into designing efficient datapaths for such computations [42] (a detailed review is given in Chapter 5). The design problem is non-trivial and many of the previously proposed approaches are sub-optimal since they derive solutions based on greedy heuristics. Chapter 5 discusses these issues in detail and proposes a set of electronic design automation (EDA) algorithms that specifically tackle the resource allocation optimisation problem for Constant Ma-

trix Multiplication (CMM) operations Such algorithms are important given the large amount of mobile applications that are built with fundamental CMM operations

# 13 Research Objectives

The research goals of this thesis may be summarised as follows

- 1 To design and implement energy-efficient hardware architectures for the SA-DCT and the SA-IDCT

- 2 Verify that both architectures conform to the official MPEG-4 standard requirements by comparing the bitstreams of a software-only MPEG-4 codec to an MPEG-4 codec that computes the SA-DCT/IDCT using the proposed hardware architectures

- 3 To derive a power and energy normalisation framework that facilitates fair benchmarking of competing architectures. Benchmarking is difficult due to the unavailability of source code for the prior art and the fact that in general other approaches are implemented in different technologies. For these reasons, some normalisations are required to justify any comparisons made

- 4 Using the derived framework, evaluate both architectures against the prior art in the literature in terms of area, speed, power and energy

- 5 To design and implement a hardware resource allocation algorithm for a general constant matrix multiplication operation (of which the SA-DCT/IDCT are particular cases)

- 6 Evaluate the proposed CMM algorithm against prior art proposed in the literature

# 14 Thesis Structure

This thesis is structured as follows

• Chapter 1 – Introduction

The introduction (this chapter) outlines the motivations for the research proposed in this thesis providing a global context. The scope and objectives of the work are clearly outlined

• Chapter 2 - Technical Background

The technical background chapter outlines a more in-depth technical context for the work. The general topics covered are digital video processing (in particular transform based-compression and object-based processing) and low power design (power dissipation phenomena, power analysis techniques and low power design techniques). A high level justification is also given for the CMM optimisation algorithm proposed in Chapter 5.

• Chapter 3 – SA-DCT Architecture

The SA-DCT chapter provides a review of prior hardware implementations for the SA-DCT. The proposed SA-DCT architecture is subsequently described in detail. This is followed by conformance testing results and evaluation against the prior art.

#### • Chapter 4 – SA-IDCT Architecture

The SA-IDCT chapter provides a review of prior hardware implementations for the SA-IDCT, with special emphasis on the distinctions between the SA-DCT and the SA-IDCT The proposed SA-IDCT architecture is subsequently described in detail. This is followed by conformance testing results and evaluation against the prior art

#### • Chapter 5 – Dot Product High Level Synthesis

This chapter firstly outlines the taxonomy of multiplication by constant applications to illustrate where the CMM operation sits in relation to other similar operations. This is followed by a characterisation of the dimensionality of the CMM optimisation problem parameters and a survey of prior art with these parameters in mind. Subsequently, the proposed optimisation algorithm is described in detail followed by experimental results that justify the approach taken and facilitate evaluation against relevant prior art.

#### • Chapter 6 - Conclusions & Future Work

A summary of the main results achieved in Chapters 3, 4 and 5 is presented. This is followed by a discussion of possible future research ideas to improve and/or extend the work presented in this thesis.

### • Appendix A - Leaf-Labelled Complete Rooted Binary Trees

This appendix provides some mathematical proofs that are related to the permutation space modelling of the proposed CMM optimisation algorithm in Chapter 5. In high-level terms, the permutations are related to the number of two input adder topologies possible for a generic multi-operand addition. Then, for each topology, the task is to find how many different ways there are of mapping addends to input pins, such that the resultant injective mapping from the set of input pins to the set of 'network adder output pins' is unique. Essentially, the issue is finding out how many different associative combinations of two addends are possible while ensuring duplicates due to the commutative property of addition are not counted.

# 15 Summary

We are currently witnessing the convergence of many diverse applications (communication, multi-media, internet, etc.) onto a mobile platform. Users constantly demand the conflicting goals (from a system design perspective) of enhanced performance and longer battery life. Mobile digital video applications are certain to emerge in the near future, especially given that many of the key hardware components such as colour display, camera sensor and memory card are already present in the popular camera phones of today. It is estimated that by 2009, more than 31 million Americans will use video messaging generating 5.4B USD in revenue [43]. The key challenges facing the engineering community have been outlined in this chapter and it is clear that there are two dominant underpinning paradigms – efficient video compression and efficient hardware design. This work aims to help in this regard by proposing efficient multimedia co-processors (SA-DCT, SA-IDCT) and a set of algorithms that aid the design of a dominant general DSP operation – the constant matrix multiplication (of which the SA-DCT and SA-IDCT are particular cases)

## 2.1 Introduction

This chapter gives a technical overview of digital video processing and low power design to provide context for the research in subsequent chapters. The starting point for this thesis was to investigate power efficient hardware implementations for the SA-DCT/IDCT algorithms suitable for mobile devices (see Chapter 3 and Chapter 4). Research in this has led the author to realise that the SA-DCT/IDCT are instances of a more general task in DSP and video processing—the constant matrix multiplication (CMM). Since CMMs are a common task, and power optimisation is vital, this has led the author to research an electronic design automation (EDA) algorithm capable of optimising the hardware for a general CMM task (see Chapter 5). The algorithm can be leveraged when implementing any application that uses CMM tasks.

Digital video applications are primed to become mainstream on the emerging convergent mobile platform as discussed in Chapter 1. This chapter outlines why digital video requires complex compression algorithms and gives a detailed overview of the theoretical foundations of these algorithms and the associated industry standards (see Section 2.2). MPEG-4 object-based compression, which requires the computationally intensive SA-DCT and SA-IDCT algorithms, is discussed in Section 2.2.5. With the application and algorithmic foundations outlined, there then follows a survey of approaches to implementing such complex compression schemes on mobile embedded platforms which have extremely limited energy sources. As more features are integrated on the convergent device, the strain on its battery increases. This is problematic since consumers demand the conflicting goals of more features and increased battery life. Because power consumption properties are so important, a comprehensive survey of the sources of power consumption in CMOS circuitry is given along with the most popular techniques for estimating and tackling this issue (see Section 2.3).

# 2.2 Digital Video Processing

Prior to discussing how video data is processed, it is essential to understand how an electrical representation of a video sequence is formed [44]. At the most basic level an analogue image signal is generated

when a camera scans a two-dimensional scene and converts it into an electrical signal. A video signal consists of several successive image scans where each image is referred to as a frame. The scanning process actually generates three signals for each frame corresponding to the primary colours red (R), green (G) and blue (B). To generate a digital image, each of the RGB signals are sampled and then quantised to a certain number of bits (usually eight) per sample. Each quantised sample is referred to as a pixel or pel and these are the fundamental unit of image processing and analysis. A frame is therefore a rectangular 2D array of pels where each pel location has three eight-bit values — one for each of the RGB colour components at that location

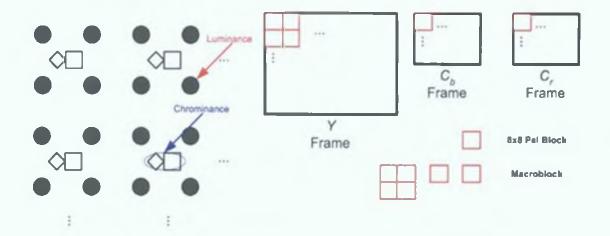

RGB signals are usually transformed into another colour space called  $YC_bC_r$  where the Y signal represents the luminance (or brightness) component of the image whilst the  $C_b$  and  $C_r$  components represent the chrominance (or colour) components. This facilitates compatibility with black and white video but also helps compression since  $C_b$  and  $C_r$  are amenable to sub-sampling as discussed subsequently. The transformation equations are outlined in Equation 2.1

$$\begin{bmatrix} Y \\ C_b \\ C_r \end{bmatrix} = \begin{bmatrix} 0.257 & 0.504 & 0.098 \\ -0.148 & -0.291 & 0.439 \\ 0.439 & -0.368 & -0.071 \end{bmatrix} \begin{bmatrix} R' \\ G' \\ B' \end{bmatrix}$$

(2.1)

R'G'B' refers to the gamma-corrected version of the RGB colour space. Gamma-correction is a necessary step to ensure that an image is displayed accurately on a computer screen. All monitors scale input pixel voltages depending on their gamma function when displaying to a screen so the original RGB input voltages must be adjusted to R'G'B' to counteract the effect

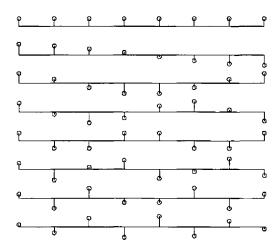

Most applications require standardised video formats, of which there are many. One example is the Common Intermediate Format (CIF), which has a luminance (Y) frame resolution of  $352 \times 288$  pels with a frame rate of 30Hz $^1$ . The chrominance bandwidths are half that of the luminance since the human visual system is less sensitive to chrominance information [44]. CIF is an example of the 4 2 0 image format – here the chrominance components are sub-sampled by a ratio of two horizontally and by a ratio of two vertically as shown in Figure 2.1. A 4 2.0 frame is composed of three planes (one for each of Y,  $C_b$  and  $C_\tau$ ) as illustrated in the figure, and these planes are usually passed to video processing tools in sequence when processing the frame. Each plane is sub-divided into non-overlapping 2D blocks of 8 × 8 pels. For every four Y blocks there are two chrominance blocks – one for each of  $C_b$  and  $C_\tau$  (if the format is 4.2.0). Each group of corresponding six blocks is referred to as a macroblock as illustrated in Figure 2.1. In a single CIF frame there are 396 (22 × 18) macroblocks

Chrominance sub-sampling is the first step taken in compressing the video data without any loss perceptible to the human eye. However, further compression of video data is necessary when you consider that the bit rate for uncompressed CIF is approximately 4 5MB/s (152064 bytes per frame × 30 frames per second)! The remainder of this section summarises the techniques used to compress video into the most compact form possible for storage or transmission over a network to a compatible decoder. Typically, compression ratios are traded off against decoded video quality and the acceptable quality depends on the application, but it is usually possible to compress video data to a very high degree with only minor

<sup>&</sup>lt;sup>1</sup>The lower resolution Quarter Common Intermediate Format (QCIF) has a Y component resolution of 176 × 144

<sup>&</sup>lt;sup>2</sup>This thesis primarily concentrates on DCT based codecs – wavelet based compression codecs (as used in JPEG-2000) are only briefly described

Figure 2.1: The 4:2:0 Image Format

quality degradation.

The achievement of high compression ratios for video data is made possible primarily because of the huge amount of redundancy present in such data. These redundancies may be broadly classified as follows:

- Spatial Redundancy Taking a single frame in isolation, it is highly probable that neighbouring

pixels are highly correlated.

- Temporal Redundancy Most of the time it is likely that successive frames will be very similar in terms of their pixel content.

- Perceptual Redundancy The human visual system is less sensitive to high frequency information [44].

The above are very intuitive properties but they can be exploited by very powerful compression techniques to remove as much redundant data as possible with minimal degradation of perceptual decoded quality for efficient transmission or storage. The amount of compression acceptable depends on the target application. In some cases (such as medical imaging) it is necessary that the decoded image be identical to the original image prior to encoding. This is called lossless coding, and hence redundancy can only be exploited to a limited extent. In lossy coding applications the compression can be more aggressive if defects in the decoded image are permitted. Again, the acceptable level of degradation depends on the target application and also the available bandwidth. In a low bit rate mobile environment it may be necessary to sacrifice some quality to ensure the compression rates are high enough to guarantee real time decoding.

# 2.2.1 A Generic Video Compression System

This section will briefly explain how a general video compression scheme works to illustrate how the redundancies outlined previously are exploited. The concept behind the system as a whole is explained and each of the tools involved are introduced. It is not the intention of this document to discuss each tool

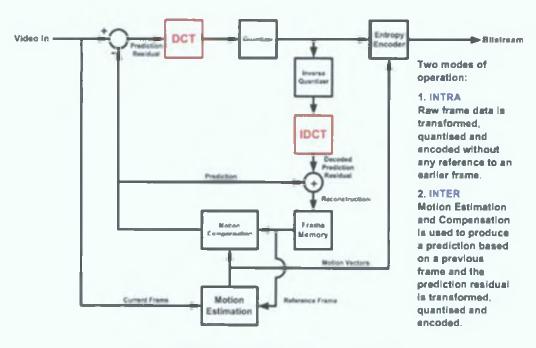

Figure 2.2: A Generic Video Compression Codec

Figure 2.3: Intra Mode Coding Flow

in depth as each are worthy research topics in their own right. The author's work focuses on the object-based derivative of the Discrete Cosine Transform (DCT) tool and this section gives a system context for the DCT. The DCT itself is given an in-depth treatment in Section 2.2.3.

A generic video coder/decoder (codec) is illustrated in Figure 2.2 [45]. A system like this is commonly referred to as a hybrid coder as it employs a combination of intraframe (transform-based compression) and interframe (differential pulse code modulation (DPCM) theory) techniques. The interframe processing stage exploits temporal redundancy and this is followed by intraframe coding, which exploits the spatial and perceptual redundancy of the result.

### 2.2.1.1 Intraframe Compression

Intraframe coding means that the frame is coded without any references to other frames. In relation to the codec in Figure 2.2, the feedback loop is not used in intra mode and the equivalent system is illustrated in Figure 2.3. If a frame is to be intra coded, it is fed to the above system in non-overlapping  $8 \times 8$  pel blocks. Each of the blocks for all planes undergoes transformation, quantisation and entropy encoding. Recall that each frame has a Y,  $C_0$  and  $C_r$  plane and these planes are usually processed in turn per macroblock in a horizontal raster order.

8 × 8 Block Transform The transform tool exploits spatial and perceptual redundancy in a frame. It maps spatial pel data to the frequency domain where each transform coefficient represents a spatial

Figure 2 4 Zigzag Scan Order

frequency from DC up to the Nyqvist limit. The reason for doing this stems from the fact that the image energy of most natural scenes is concentrated in the low frequency region and that humans are less sensitive to high frequency information. This suggests that operating in the frequency domain may make compression operations easier. Therefore the transform block converts data to the frequency domain to make subsequent quantisation and coding more efficient. This is achieved by decorrelating-correlating the signal energy (Section 2.2.2 explains this in much greater depth). The transform usually used for image and video coders is the Discrete Cosine Transform (DCT).

Quantiser It should be noted that the transform block does not achieve any compression in isolation – it merely converts the data to an alternate representation. Subsequent quantisation and variable length coding give the necessary bit rate reduction. Since the higher frequency coefficients are less important and have quite low values, they can be more coarsely quantised and may indeed be quantised to zero. Depending on the activity in the block, it may only be necessary to retain the DC value and a few low frequency coefficients as opposed to all 64 pel values without affecting the decoded frame quality. More detailed information on quantisers and quantiser design may be found in [44, 45, 46]

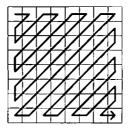

Variable Length Encoder To achieve further compression, the quantised transform coefficients undergo variable length coding (VLC) The idea behind VLC is that the length of the code assigned should vary inversely with the probability of occurrence of that code thus reducing the amount of bits required to represent the information [45] The first step involves zigzag scanning (as shown in Figure 2 4) and run-length coding of the quantised transform coefficients (referred to as symbols in information theory parlance) into coding events. These coding events have lower entropy than the original symbols. The quantised coefficients are zigzag scanned in order of ascending frequency since there is a high probability that the high frequency coefficients will be long runs of zeros after quantisation. The next step is referred to as source coding, which involves replacing the coding events with binary codewords, the length of which depends on their probability of occurrence [44]. The most commonly used source coding schemes are Huffman Coding and Arithmetic Coding [44]. The VLCs generated for each block are then routed out to the bit-stream where the system level controller multiplexes them as appropriate.

#### 2 2 1 2 Interframe Compression

To exploit the temporal redundancy in video data, the codec in Figure 2.2 operates in inter mode. A prediction of the current frame is formed (using a technique called motion estimation and compensation) and the prediction residual is then coded using the techniques outlined in the previous section. This is

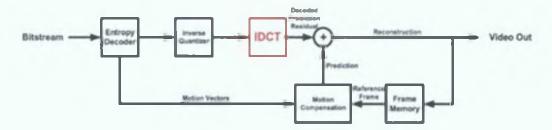

Figure 2.5: A Generic Video Decoder

done because the entropy of the prediction residual is much lower than that of the frame itself - this is especially true at high frame rates when successive frames are likely to be almost identical.

Generating the Reconstructed Reference Frame – The Decoder — To create a prediction for a current frame based on one or more reference frames it is inappropriate to use the raw uncompressed data as a reference. The reference frames used must be identical to the frames that will be reconstructed in the decoder. This is because the prediction generated in the encoder must be identical to that generated in the decoder in order for the coded prediction residual that is transmitted to be appropriate in both systems. As a consequence, a decoder must also be present in the encoder – hence the name codec (coder/decoder). A generic video decoder is shown in Figure 2.5. To create a decoded prediction residual the data must undergo the opposite operations to the intra coding operations (i.e. Variable Length Decoding (VLD), inverse quantisation and an inverse transformation). This residual is added to the prediction (inter mode only) to generate the reconstructed frame. It is intuitive to see how the decoder in Figure 2.5 fits into the feedback loop in the codec in Figure 2.2.

Motion Estimation and Compensation Given a current frame and a reference frame<sup>3</sup> (a previously reconstructed frame) a prediction is formed for the current frame by using motion estimation and compensation. The motion estimation tool starts by loading the current frame into memory and processes the frame on a macroblock-by-macroblock basis. For each  $16 \times 16 Y$  component of the macroblock in the current frame, the tool searches a certain region of the reference frame for the closest match. The search strategy used can vary and some examples include [47]:

- Full Search

- Logarithmic Search

- Hierarchical Search

This match is evaluated using a block-matching algorithm (BMA). Some of the more popular BMAs include:

- Cross Correlation Function (CCF)

- Mean-Squared Error (MSE)

The reference frame is typically the previous frame in the video sequence, although some standards (e.g. MPEG-1, MPEG-2 & MPEG-4) allow predictions based on future frames.

Figure 2.6: Motion Estimation and Compensation

- Mean Absolute Difference (MAD)

- Sum of Absolute Differences (SAD)

The motion estimation tool searches the reference data search window for the corresponding  $16 \times 16$  macroblock component with the best value according to the adopted BMA. In general this macroblock component will not be at the same coordinates as the current macroblock component so a motion vector (MV) is calculated to represent the offset. To generate the prediction frame (or motion compensated frame) for the current frame the MVs for each macroblock are used to translate the associated macroblock component with the best match in the reference frame to the location of the current macroblock component in the current frame. This process is more clearly illustrated in Figure 2.6 [44].

The motion compensated frame is the prediction of the current frame and this is subtracted from the current frame to create the prediction residual as shown in Figure 2.2. The prediction residual based upon motion estimation and compensation in general will have much lower entropy than a prediction residual formed by a simple frame difference. As a consequence, the temporal redundancy of the data is extensively exploited resulting in improved compression efficiency. To be clear – the outputs from the motion estimation and compensation tool are a predicted frame and a set of motion vectors (one for each macroblock). These MVs then undergo entropy coding and the VLCs produced are multiplexed appropriately into the output bit-stream. As shown in Figure 2.2, the prediction residual is encoded using the DCT-based intraframe processing steps. This fact re-enforces the importance of the DCT operation in a video compression system. Usually the BMA is evaluated for the Y component of each macroblock only and a scaled version of the resulting MV is assigned to the corresponding chrominance components when generating the chrominance motion compensated frame planes. Motion estimation and compensation is the most computationally demanding task in a video codec and a survey of power

#### 2 2 1 3 Inter/Intra Mode Decision